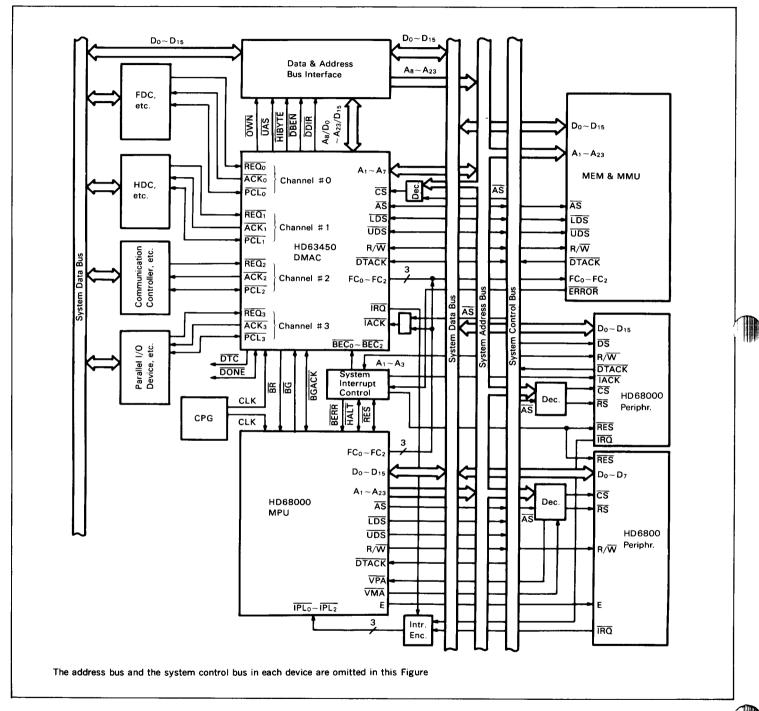

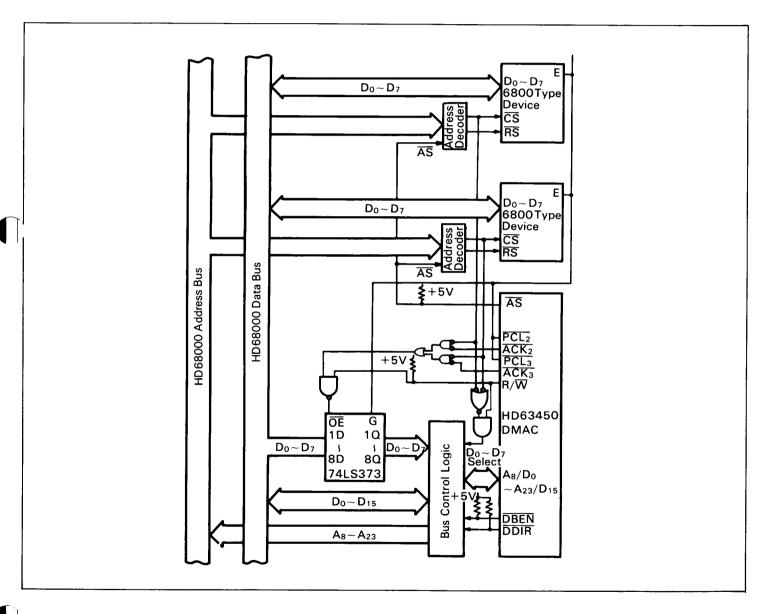

# HD63450, HD63450Y, HD63450P HD63450PS, HD63450CP CMOS Direct Memory Access Controller

SEPTEMBER, 1989

# 🕲 HITACHI

The HD63450 is a CMOS Direct Memory Access Controller (DMAC). It is upwardly compatible with the NMOS DMAC HD68450.

In addition to the NMOS DMAC HD68450 features, the HD63450 performs one or several blocks of data transfer (Operand; byte, word, or long word) between memory and peripheral device at high speed. The block transfer restart operation is provided (Multi-Block Transfer with  $\overline{\rm DONE}$  Mode). The number of operands in a block is determined by a transfer count.

Fabricated in CMOS for lower power dissipation.

#### **■ FEATURES**

- HD 68000 Bus Compatible

- •4 independent DMA Channels with Programmable Priority

- Memory-to-Memory, Memory-to-Device, Device-to-Memory

Transfers

- Programmable 8-Bit or 16-Bit I/O Device Types

- Auto-Request and External-Request Transfer Modes

- Interface Lines for Requesting, Acknowledging, and Incidental Control of the Peripheral Devices

- Block Transfer Operation

In Single-Block:

- Unchaining Transfer

- Continue Mode Transfer

- Array-Chaining and Linked-Array-

- Chaining Transfers

- Multi-Block Transfer with DONE

- ●68000 Bus Exception Processing Support

- ●2 Vectored Interrupts for each Channel

- Variable System Bus Bandwidth Rate Utilization

- Fast Transfer Rates: Up to 6.25 Mbytes/sec. at 12.5 MHz

- CMOS +5 Volts Operation

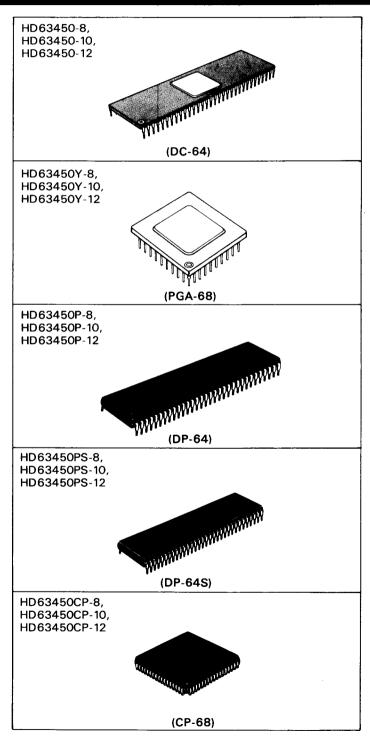

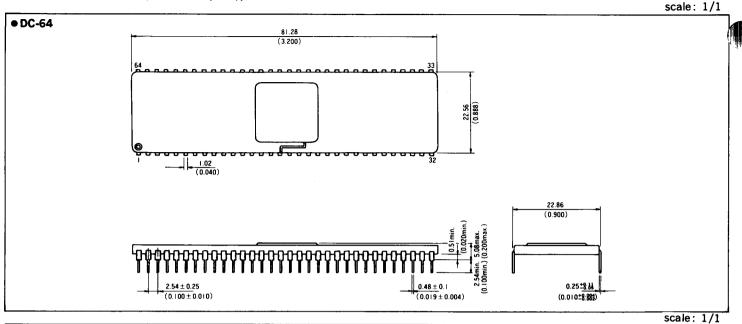

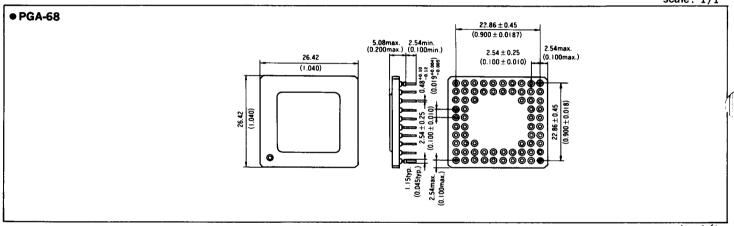

# TYPE OF PRODUCTS

| Type No.     | Bus Timing | Packaging |  |  |

|--------------|------------|-----------|--|--|

| HD63450-8    | 8MHz       |           |  |  |

| HD63450-10   | 10MHz      | DC-64     |  |  |

| HD63450-12   | 12.5MHz    | ]         |  |  |

| HD63450Y-8   | 8MHz       |           |  |  |

| HD63450Y-10  | 10MHz      | PGA-68    |  |  |

| HD63450Y-12  | 12.5MHz    |           |  |  |

| HD63450P-8   | 8MHz       |           |  |  |

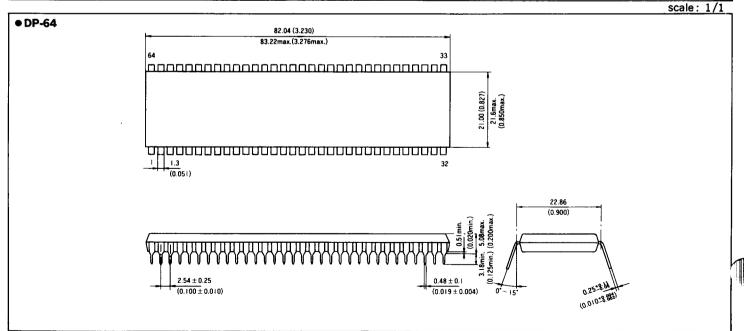

| HD63450Y-10  | 10MHz      | DP-64     |  |  |

| HD63450Y-12  | 12.5MHz    |           |  |  |

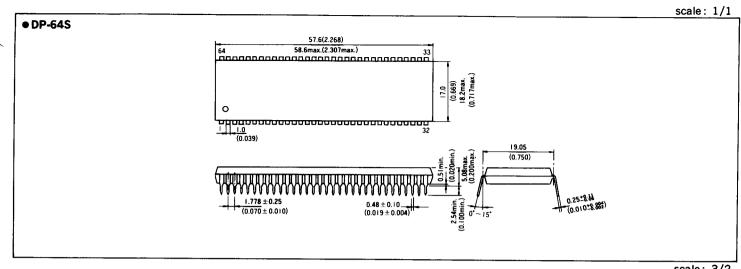

| HD63450PS-8  | 8MHz       |           |  |  |

| HD63450PS-10 | 10MHz      | DP-64S    |  |  |

| HD63450PS-12 | 12.5MHz    | ]         |  |  |

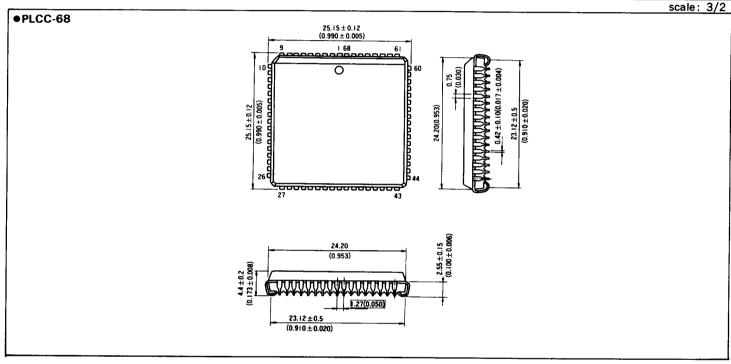

| HD63450CP-8  | 8MHz       |           |  |  |

| HD63450CP-10 | 10MHz      | CP-68     |  |  |

| HD63450CP-12 | 12.5MHz    |           |  |  |

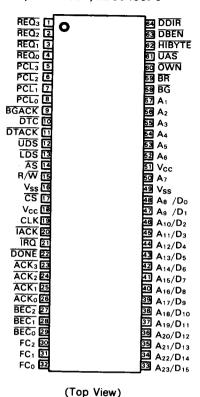

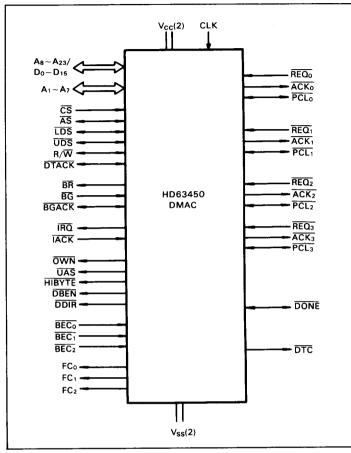

# ■ PIN ARRANGEMENT • HD63450, HD63450PS

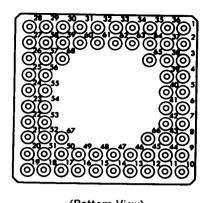

# ● HD63450Y

#### (Bottom View)

| Pin No. | Function         | Pin No. | Function                         | Pin No. | Function                       | Pin No. | Function                        |

|---------|------------------|---------|----------------------------------|---------|--------------------------------|---------|---------------------------------|

| _1      | N/C              | 18      | PCL <sub>1</sub>                 | 35      | A19/D11                        | 52      | BGACK                           |

| 2       | A13/D5           | 19      | DTACK                            | 36      | A17/D9                         | 53      | LDS                             |

| 3       | A11/D3           | 20      | UDS                              | 37      | A15/D7                         | 54      | Vss                             |

| 4       | A10/D2           | 21      | ĀS'                              | 38      | A12/D4                         | 55      | Vcc                             |

| 5       | Aa/Do            | 22      | R/W                              | 39      | A <sub>9</sub> /D <sub>1</sub> | 56      | DONÉ                            |

| 6       | A7               | 23      | N/C                              | 40      | Vss                            | 57      | IRQ                             |

| 7       | A <sub>6</sub> . | 24      | CS                               | 41      | Vcc                            | 58      | ACK <sub>2</sub>                |

| 8       | <b>A</b> 5       | 25      | CLK                              | 42      | A4                             | 59      | BEC <sub>2</sub>                |

| 9       | A <sub>3</sub>   | 26      | IACK                             | 43      | Az                             | 60      | BEC <sub>0</sub>                |

| 10      | N/C              | 27      | ACK₃                             | 44      | BG                             | 61      | FC <sub>0</sub>                 |

| 11      | BR               | 28      | ACK <sub>0</sub>                 | 45      | ŌWN                            | 62      | A21/D13                         |

| 12      | UAS              | 29      | BEC <sub>1</sub>                 | 46      | HIBYTE                         | 63      | A18/D10                         |

| 13      | DBEN             | 30      | FC <sub>2</sub>                  | 47      | DDIR                           | 64      | A <sub>16</sub> /D <sub>8</sub> |

| 14      | REQ₃             | 31      | FC <sub>1</sub>                  | 48      | REQ <sub>1</sub>               | 65      | A14/D6                          |

| 15      | ŘEQ₂             | 32      | A23/D15                          | 49      | PCL <sub>2</sub>               | 66      | A <sub>1</sub>                  |

| 16      | REQ <sub>0</sub> | 33      | A22/D14                          | 50      | PCLo                           | 67      | DTC                             |

| 17      | PCL <sub>3</sub> | 34      | A <sub>20</sub> /D <sub>12</sub> | 51      | N/C                            | 68      | ACK <sub>1</sub>                |

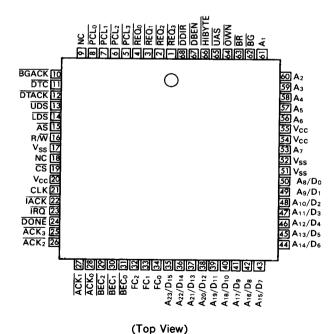

### ● HD63450CP

( HITACHI

# ■ ABSOLUTE MAXIMUM RATINGS

| Item                        | Symbol            | Value                     |          |

|-----------------------------|-------------------|---------------------------|----------|

| Supply Voltage              | V <sub>CC</sub> * |                           | Unit     |

| Input Voltage               |                   | -0.3~+7.0                 | <b>V</b> |

|                             | V <sub>in</sub> * | -0.3~V <sub>cc</sub> +0.3 | V        |

| Operating Temperature Range | T <sub>opr</sub>  | 0~+70                     | °C       |

| Storage Temperature         | T <sub>stg</sub>  | -55~+150                  |          |

| A Cal                       |                   | 33 - 1130                 | °C       |

<sup>\*</sup>With respect to VSS (SYSTEM GND)

(NOTE) Permanent damage to the device may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of the device.

# RECOMMENDED OPERATING CONDITIONS

| item                             | Symbol                                            | min  | da em |      |          |

|----------------------------------|---------------------------------------------------|------|-------|------|----------|

| Supply Voltage                   |                                                   |      | typ   | max  | Unit     |

| oupply voltage                   | Vcc*                                              | 4.75 | 5.0   | 5.25 | ٧        |

| Input Voltage                    | V <sub>IH</sub> *                                 | 2.0  |       | Vcc  |          |

|                                  | V <sub>IL</sub> *                                 | -0.3 |       | 0.8  | V        |

| Operating Temperature            | Topr                                              | 0    | 25    | 70   | <u>·</u> |

| With respect to Vss (SYSTEM CND) | —— <del>———————————————————————————————————</del> |      |       | /0   | C        |

# ■ ELECTRICAL CHARACTERISTICS

# $\bullet$ DC CHARACTERISTICS (V<sub>CC</sub>=5V $\pm$ 5%, V<sub>SS</sub>=0V, T<sub>a</sub>=0 $\sim$ +70°C, unless otherwise noted.)

|                                       | Item                                                                                                                                                                                                                                                      | Symbol           | Test Condition                                        | min                  | typ | max | Unit |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------|----------------------|-----|-----|------|

| Input "High" Voltage                  |                                                                                                                                                                                                                                                           | ViH              |                                                       | 2.0                  | -34 | Vcc | V    |

| Input "Low" Voltage                   |                                                                                                                                                                                                                                                           | VIL              |                                                       | V <sub>SS</sub> -0.3 |     | 0.8 | V    |

| Input Leakage Current                 | CS, IACK, BG, CLK, BEC <sub>0</sub> ~BEC <sub>2</sub> REQ <sub>0</sub> ~REQ <sub>3</sub>                                                                                                                                                                  | lin              |                                                       | V33 0.3              |     | 10  | μΑ   |

| Three-State (Off State) Input Current | A <sub>1</sub> ~A <sub>7</sub> , D <sub>0</sub> ~D <sub>15</sub> /A <sub>8</sub> ~A <sub>23</sub> ,<br>AS, UDS, LDS, R/W, UAS,<br>DTACK, BGACK, OWN, DTC,<br>HIBYTE, DDIR, DBEN,<br>FC <sub>0</sub> ~FC <sub>2</sub> , PCL <sub>0</sub> ~PCL <sub>3</sub> | I <sub>TSI</sub> |                                                       |                      |     | 10  | μΑ   |

| Open Drain (Off State) Input Current  | IRQ, DONE                                                                                                                                                                                                                                                 | lopi             |                                                       |                      |     | 20  | μA   |

| Output "High" Voltage                 | A1~A7, D0~D15/A8~A23,  AS, UDS, LDS, R/W, UAS,  DTACK, BGACK, BR, OWN,  DTC, HIBYTE, DDIR, DBEN,  ACK0~ACK3, PCL0~PCL3,  FC0~FC2                                                                                                                          | Vон              | Іон = — 400 µ A                                       | Vcc - 2.0            |     |     | V    |

|                                       | A <sub>1</sub> ~A <sub>7</sub> , FC <sub>0</sub> ~FC <sub>2</sub>                                                                                                                                                                                         | Vol              | I <sub>OL</sub> = 3.2mA                               |                      |     | 0.5 |      |

| Output "Low" Voltage                  | D <sub>0</sub> ~D <sub>15</sub> /A <sub>8</sub> ~A <sub>23</sub> , AS, UDS,<br>LDS, R/W, DTACK, BR,<br>OWN, DTC, HIBYTE, DDIR,<br>DBEN, ACK <sub>0</sub> ~ACK <sub>3</sub> , UAS,<br>PCL <sub>0</sub> ~PCL <sub>3</sub> , BGACK                           | Vot              | loL=5.3mA                                             |                      |     | 0.5 | V    |

|                                       | IRQ, DONE                                                                                                                                                                                                                                                 | Vol              | loL=8.9mA                                             |                      |     | 0.5 |      |

| Power Dissipation                     |                                                                                                                                                                                                                                                           | P <sub>D</sub>   | f=8MHz, V <sub>CC</sub> =5.0V<br>T <sub>a</sub> =25°C |                      | 0.5 | 1.0 | w    |

| Capacitance                           |                                                                                                                                                                                                                                                           | Cin              | V <sub>in</sub> =0V<br>T <sub>a</sub> =25°C, f=1MHz   |                      |     | 15  | рF   |

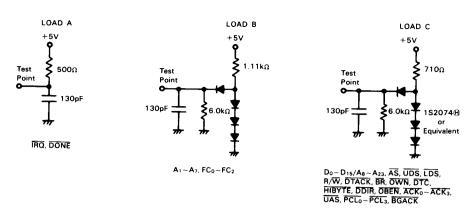

Figure 1 Test Loads

# ullet AC ELECTRICAL SPECIFICATIONS (Vcc=5V±5%, Vss=0V, Ta=0 $\sim$ +70°C, unless otherwise noted.)

| Frequency of Operation   f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                                         |         |                   | 81              | ИНz         | 10  | MHz   | 12.      | 5MHz  | T        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|---------|-------------------|-----------------|-------------|-----|-------|----------|-------|----------|

| Frequency of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No. | Item                                    | Symbol  | Test<br>Condition | Ve <sub>1</sub> | rsion       | Ve  | rsion | Ve       | rsion | Unit     |

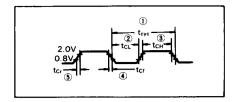

| 1   Clock Period   Leye   Clock Width Low   Clot   Low   Clot     |     |                                         |         |                   | min             | max         | min | max   | min      | max   |          |

| Clock Width Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                         | f       |                   | 4.0             | 8.0         | 4.0 | 10.0  | 4.0      | 12.5  | MHz      |

| Clock Width High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                                         | tcyc    |                   | 125             | 250         | 100 | 250   | 80       | 250   | ns       |

| Clock Fill Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                         | tcL     | ]                 | 55              | 125         | 45  | 125   | 35       | 125   | ns       |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | <u> </u>                                | tсн     |                   | 55              | 125         | 45  | 125   | 35       | 125   | ns       |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                                         | tcf     |                   |                 | 10          |     | 10    |          | 5     | ns       |

| To   Data in to DBEN Low   Store   Low       |     |                                         | tcr     |                   |                 | 10          |     | 10    |          | 5     | ns       |

| B   DTACK Low to Data Invalid   toTILDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                                         | tası    |                   | 20              |             | 15  |       | 15       |       | ns       |

| 9 Address in to AS in Low  10 AS, DS in High to Address in Invalid  11 Clock High to DDIR Low  12 Clock High to DDIR High  13 DS in High to DDIR High Impedance  14 Clock Low to DBEN Low  15 Clock Low to DBEN High  16 DS in High to Data Out Valid (MPU read)  17 Clock High to Data High Impedance  18 DS in High to Data High Impedance  19 DS in High to DATACK High  10 DS in High to DTACK High  110 Ins  120 Ins  130 Ins  140 Clock Low to DBEN High  151 Clock Low to DBEN High  152 Clock Low to DBEN High  153 Ins  164 DS in High to Data Out Valid (MPU read)  175 Clock High to Data Out Valid (MPU read)  186 DS in High to Data High Impedance  19 DS in High to Data High Impedance  19 DS in High to Data High Impedance  10 Clock Low to DTACK Low  11 DS in High to DATACK High  12 DTACK Width High  15 DTACK Low to DS in High  15 DTACK Low to DS in High  15 DTACK Low to DS in High  15 DTACK Low to DR Low  16 DTACK Low  17 Clock High to DTACK High Impedance  18 DS in High to DTACK High Impedance  19 DS in High to DTACK High Impedance  10 DTACK Low to DS in High  10 10 10 ns  110 ns  11 |     |                                         | tDIDBL  |                   | 0               |             | 0   |       | 0        |       | ns       |

| 10   AS, DS in High to Address in Invalid   tsihatv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |                                         | totloi  |                   | 0               |             | 0   |       | 0        | 1     | ns       |

| 10A DS in High to CS High   10SHCSH   11 Clock High to DDIR Low   1cHorl   12 Clock High to DDIR High   1cHorl   13 DS in High to DDIR High Impedance   1cSHDRZ   120   110   110   ns   15 Clock Low to DBEN Low   1cLobe   155 ns   16 DS in High to DBEN High Impedance   1cSHDRZ   120   110   110   ns   17 Clock High to Data Out Valid (MPU read)   1cHorl   120   110   110   ns   18 DS in High to Data Out Invalid   1cSHDZ   120   110   110   ns   18 DS in High to Data High Impedance   1cSHDZ   120   110   110   ns   18 DS in High to Data High Impedance   1cSHDZ   120   110   110   ns   18 DS in High to Data High Impedance   1cSHDZ   120   110   110   ns   18 DS in High to Data High Impedance   1cSHDZ   120   110   110   ns   18 DS in High to DATACK Low   1cLotl   170   60   55 ns   18 DS in High to DATACK High Impedance   1cSHDZ   120   110   110   ns   110   ns   120   110   110   ns   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   120   12   |     |                                         | TAIASL  | ]                 | 0               |             | 0   |       | 0        |       |          |

| 11   Clock High to DDIR Low   Clkper   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1.0   1   |     |                                         | tsihaiv |                   | 0               |             | 0   |       | 0        |       | ns       |

| 12   Clock High to DDIR High   10   DDIR High   TOHORH     13   DS in High to DDIR High Impedance   10   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   1   |     |                                         | tознозн | 1                 |                 | 1.0         |     | 1.0   | clk.per. | 1.0   | clk.per. |

| 13   DS in High to DDIR High Impedance   toshdar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | Clock High to DDIR Low                  | tCHDRL  | 1                 |                 | 70          |     | 60    |          | 55    | ns       |

| 14   Clock Low to DBEN Low   15   Clock Low to DBEN High   15   Clock Low to DBEN High   16   DS in High to DBEN High Impedance   15   Clock High to Data Out Valid (MPU read)   16   Clock High to Data Out Invalid   160   140   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110     |     |                                         | tchdrh  | ]                 |                 | 70          |     | 60    |          | 55    | ns       |

| 15   Clock Low to DBEN High   10   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110     |     |                                         | toshorz | rigurei           |                 | 120         |     | 110   |          | 110   | ns       |

| 15   Clock Low to DBEN High   10   DS in High to DBEN High Impedance   10   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110      |     |                                         | tCLDBL  |                   |                 | 70          |     | 60    |          | 55    |          |

| 16         DS in High to DBEN High Impedance         tDSHDBZ           17         Clock High to Data Out Valid (MPU read)         tCHDVM           18         DS in High to Data Out Invalid         tDSHDZ           19         DS in High to Data High Impedance         tDSHDZ           20         Clock Low to DTACK Low         tCLDTL           21         DS in High to DTACK High         tDSHDTH           22         DTACK Width High         tDTH           23         DS in High to DTACK High Impedance         tDSHDTZ           24         DTACK Low to DS in High         tDTLDSH           25         REQ Width Low         tREQL           26         REQ Low to BR Low         tRELBRL           27         Clock High to BR Low         tCHBRL           28         Clock High to BR High         tCHBRH           29         BG Low to BGACK Low         tBGLBL           30         BR Low to MPU Cycle End (AS in High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15  |                                         | tCLDBH  | ~                 |                 | 70          |     | 60    |          | 55    | ns       |

| 17   Clock High to Data Out Valid (MPU read)   18   DS in High to Data Out Invalid   10SHDZn     19   DS in High to Data High Impedance   10SHDZ     20   Clock Low to DTACK Low   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110     | 16  |                                         | toshobz |                   |                 | 120         |     | 110   |          |       |          |

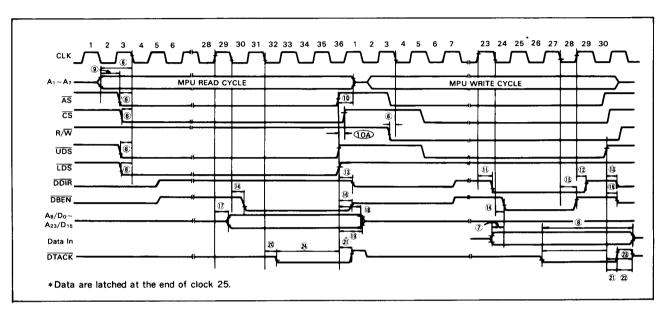

| 18         DS in High to Data Out Invalid         toshoz         0         0         0         ns           19         DS in High to Data High Impedance         toshoz         120         110         110         ns           20         Clock Low to DTACK Low         tclotl         70         60         55         ns           21         DS in High to DTACK High         toshoth         110         110         110         ns           22         DTACK Width High         toth         10         10         10         ns           23         DS in High to DTACK High Impedance         toshotz         180         160         160         ns           24         DTACK Low to DS in High         tothoth         0         0         0         ns           25         REQ Width Low         trequence         2.0         2.0         2.0         clk.per.           26         REQ Low to BR Low         trelbru         250         200         160         ns           27         Clock High to BR High         tchbr         70         60         55         ns           28         Clock High to BGACK Low         tbsLbl         4.5         4.5         4.5         clk.per.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17  | Clock High to Data Out Valid (MPU read) | tсночм  | Figure8           |                 | 180         |     | 160   |          |       |          |

| 19       DS in High to Data High Impedance       toshdz       120       110       110       ns         20       Clock Low to DTACK Low       tclotl       70       60       55       ns         21       DS in High to DTACK High       toshdth       110       110       110       ns         22       DTACK Width High       toth       10       10       10       ns         23       DS in High to DTACK High Impedance       toshdtz       180       160       160       ns         24       DTACK Low to DS in High       tothlosh       0       0       0       ns         25       REQ Width Low       treequ       2.0       2.0       2.0       clk.per.         26       REQ Low to BR Low       trelbrac       250       200       160       ns         27       Clock High to BR Low       tchbr       70       60       55       ns         28       Clock High to BR High       tchbr       70       60       55       ns         29       BG Low to BGACK Low       tbgLBL       4.5       4.5       4.5       clk.per.         30       BR Low to MPU Cycle End (AS in High)       tchchick       tchchick       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _18 |                                         | toshozn |                   | 0               |             | 0   |       | 0        |       |          |

| 20   Clock Low to DTACK Low   toLotl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19  | DS in High to Data High Impedance       | toshoz  |                   |                 | 120         |     | 110   |          | 110   |          |

| 21         DS in High to DTACK High         toshdth           22         DTACK Width High         10         10         10         ns           23         DS in High to DTACK High Impedance         toshdtz         180         160         160         ns           24         DTACK Low to DS in High         totlosh         0         0         0         ns           25         REQ Width Low         trequ         2.0         2.0         2.0         clk.per.           26         REQ Low to BR Low         trelbru         250         200         160         ns           27         Clock High to BR Low         tchbr.         70         60         55         ns           28         Clock High to BR High         tchbr.         70         60         55         ns           29         BG Low to BGACK Low         tbglb.         4.5         4.5         4.5         clk.per.           30         BR Low to MPU Cycle End (AS in High)         tbglb.         tbglb.         4.5         4.5         4.5         clk.per.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20  | Clock Low to DTACK Low                  | tCLDTL  |                   |                 | 70          |     | 60    |          |       |          |

| 22         DTACK Width High         tDTH         10         10         ns           23         DS in High to DTACK High Impedance         tDSHDTZ         180         160         160         ns           24         DTACK Low to DS in High         tDTLDSH         0         0         0         ns           25         REQ Width Low         tREQL         2.0         2.0         2.0         clk.per.           26         REQ Low to BR Low         tRELBRL         250         200         160         ns           27         Clock High to BR Low         tCHBRL         70         60         55         ns           28         Clock High to BR High         tCHBRH         70         60         55         ns           29         BG Low to BGACK Low         tBGLBL         4.5         4.5         4.5         clk.per.           30         BR Low to MPU Cycle End (AS in High)         tentacil         tentacil         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21  | DS in High to DTACK High                | toshoth |                   |                 | 110         |     | 110   |          |       |          |

| 23         DS in High to DTACK High Impedance         toshdtz         180         160         ns           24         DTACK Low to DS in High         totldsh         0         0         0         ns           25         REQ Width Low         tred         2.0         2.0         2.0         clk.per.           26         REQ Low to BR Low         trelbrich         250         200         160         ns           27         Clock High to BR Low         tohbre         70         60         55         ns           28         Clock High to BR High         tohbre         70         60         55         ns           29         BG Low to BGACK Low         tbgLbL         4.5         4.5         4.5         clk.per.           30         BR Low to MPU Cycle End (AS in High)         tbgLbL         4.5         4.5         clk.per.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22  |                                         | tотн    |                   | 10              |             | 10  |       | 10       |       |          |

| 24       DTACK Low to DS in High       totldsh       0       0       0       ns         25       REQ Width Low       treqt       2.0       2.0       2.0       clk.per.         26       REQ Low to BR Low       trelbrt       250       200       160       ns         27       Clock High to BR Low       tchbrt       70       60       55       ns         28       Clock High to BR High       tchbrh       70       60       55       ns         29       BG Low to BGACK Low       tbglbt       4.5       4.5       4.5       4.5       clk.per.         30       BR Low to MPU Cycle End (AS in High)       tbglbt       tbglbt       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23  | DS in High to DTACK High Impedance      | toshotz |                   |                 | 180         |     | 160   |          | 160   |          |

| 25         REQ Width Low         trequ         2.0         2.0         clk.per.           26         REQ Low to BR Low         trelbru         250         200         160         ns           27         Clock High to BR Low         tchbru         70         60         55         ns           28         Clock High to BR High         tchbru         70         60         55         ns           29         BG Low to BGACK Low         tbglbl         4.5         4.5         4.5         clk.per.           30         BR Low to MPU Cycle End (AS in High)         tbglbl         4.5         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24  | DTACK Low to DS in High                 | totlosh | Ì                 | 0               |             | 0   |       | 0        |       |          |

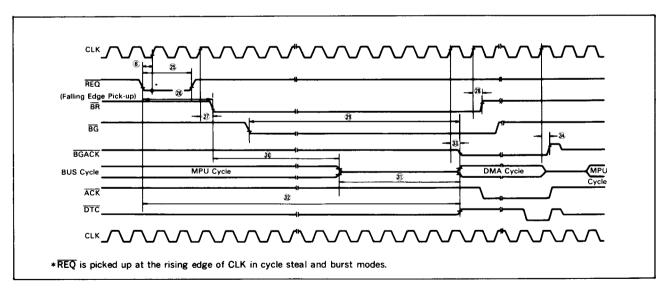

| 26       REQ Low to BR Low       trelbrian       250       200       160       ns         27       Clock High to BR Low       tchbrian       70       60       55       ns         28       Clock High to BR High       tchbrian       70       60       55       ns         29       BG Low to BGACK Low       tbglb       4.5       4.5       4.5       4.5       clk.per.         30       BR Low to MPU Cycle End (AS in High)       tbglb       10       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25  |                                         | treQL   | ľ                 | 2.0             |             | 2.0 |       |          |       |          |

| 27         Clock High to BR Low         tchbr.         70         60         55         ns           28         Clock High to BR High         tchbr.         70         60         55         ns           29         BG Low to BGACK Low         tbglb.         4.5         4.5         4.5         clk.per.           30         BR Low to MPU Cycle End (AS in High)         tbglb.         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>26</td> <td>REQ Low to BR Low</td> <td>trelbrl</td> <td>j</td> <td>250</td> <td><math>\neg \neg</math></td> <td>200</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26  | REQ Low to BR Low                       | trelbrl | j                 | 250             | $\neg \neg$ | 200 |       |          |       |          |

| 28         Clock High to BR High         tchbrh         70         60         55         ns           29         BG Low to BGACK Low         tbglbl         4.5         4.5         4.5         clk.per.           30         BR Low to MPU Cycle End (AS in High)         tbglbl         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27  |                                         | tCHBRL  |                   |                 | 70          |     | 60    | -+       | 55    |          |