# TYPES SN74LS600A THRU SN74LS603A MFMORY REFRESH CONTROLLERS

D2547, JANUARY 1981 - REVISED JUNE 1983

- Controls Refresh Cycle of 4K, 16K, and 64K Dynamic RAMs

- Creates Static RAM Appearance

- Choice of Transparent, Cycle Steal, or **Burst Refresh Modes**

- 3-State Outputs Drive Bus Lines Directly

- Critical Times Are User RC-Programmable to Optimize System Performance

| SN74LS' DW, J OR N PACKAGE   |     |       |                 |  |  |  |

|------------------------------|-----|-------|-----------------|--|--|--|

| (TOP VIEW)                   |     |       |                 |  |  |  |

| BUSY [                       | ſΤ  | J20]] | v <sub>cc</sub> |  |  |  |

| A0 [                         | ] 2 | 19 🗌  | RC BURST        |  |  |  |

| A1 [                         | ]3  | 18    | SEE TABLE       |  |  |  |

| A2 [                         | 4   | 17    | SEE TABLE       |  |  |  |

| A3 [                         | 5   | 16    | HOLD            |  |  |  |

| A4 [                         | ]6  | 15    | RAS             |  |  |  |

| A5 [                         | ]7  | 14    | REF REQ2        |  |  |  |

| A6 [                         | ]8  | 13    | REF REQ1        |  |  |  |

| SEE TABLE                    | ]9  | 12    | RC RAS LO       |  |  |  |

| GND [                        | 10  | 11    | RC RAS HI       |  |  |  |

| FOR CHIP CARRIER INFORMATION |     |       |                 |  |  |  |

CONTACT THE FACTORY

SN54LS' . . . J PACKAGE

#### SELECTION TABLE

|         |                    |             |        | MENTS       |                   |

|---------|--------------------|-------------|--------|-------------|-------------------|

| DEVICE  | REFRESH MODES      | MEMORY SIZE | PIN 9  | PIN 17      | PIN 18            |

| 'LS600A | Transparent, Burst | 4K or 16K   | 4K/16K | LATCHED RCO | RESET LATCHED RCO |

| 'LS601A | Transparent, Burst | 64K         | A7     | LATCHED RCO | RESET LATCHED RCO |

| 'LS602A | Cycle Steal, Burst | 4K or 16K   | 4K/16K | READY       | RC CYCLE STEAL    |

| 'LS603A | Cycle Steal, Burst | 64K         | A7     | READY       | RC CYCLE STEAL    |

### description

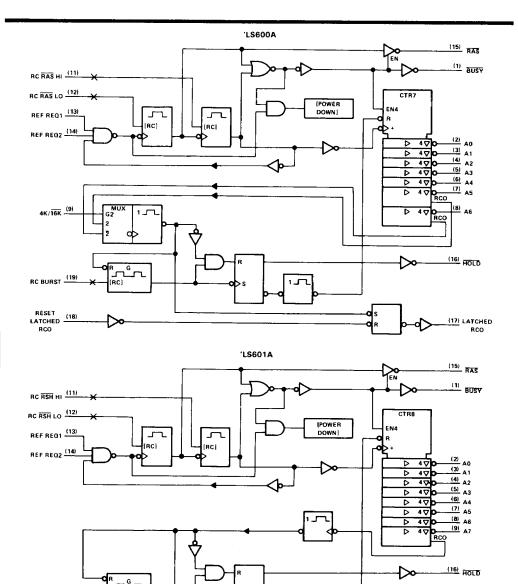

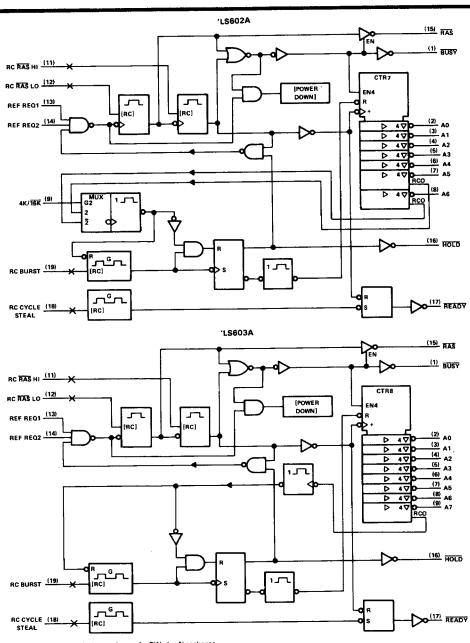

The 'LS600A thru 'LS603A memory refresh controllers contain one 8-bit synchronous counter, nine 3-state buffer drivers, four RC-controlled multivibrators, and other control circuitry on a single monolithic chip. These devices are designed to provide RAS-only refresh on 4K, 16K, and 64K dynamic RAMs. The 'LS600A and 'LS601A provide transparent refresh while the 'LS602A and 'LS603A provide cycle-steal refresh. In addition, a burst-mode timer is provided to warn the CPU that the maximum allowable refresh time is about to be violated.

#### operating modes

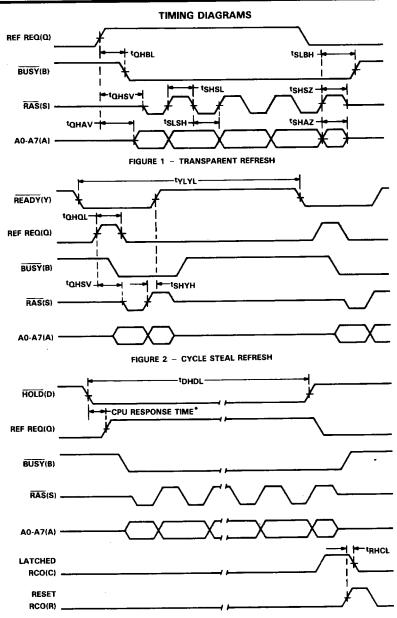

In the transparent refresh mode ('LS600A or 'LS601A), row-refresh cycles occur only during inactive CPU-memory times. In most cases the entire memory refresh sequence can be completed "transparently" without interrupting CPU operations. During idle CPU-memory periods, the REF REQ pins should be taken high so as many rows as possible can be refreshed. A low from BUSY will signal the CPU to wait until the end of that current row refresh before reinstating operations. If all row addresses have been refreshed before the burst-mode timer expires, the burst-mode timer will reset.

If the maximum allowable refresh time of the dynamic RAM is about to be exceeded, the burst mode timer will expire causing the HOLD pin to go low. This signals the CPU that a burst-mode refresh is manadatory and the burst-mode refresh will be accomplished when the CPU takes the REF REQ pins high. To ensure that all rows are refreshed, the address counter is reset to zero whenever the burst-mode timer expires. After the last row has been refreshed, the HOLD pin will return high, and the burst-mode timer will reset. The CPU can then return to normal transparent operation.

A LATCHED RCO output pin is also provided on the 'LS600A and 'LS601A to detect when the last row has been refreshed. Upon seeing a RCO from the address counter, the LATCHED RCO output will be set high. This latch is reset by providing a high-going pulse on the RESET LATCHED RCO input.

In the cycle-steal refresh mode ('LS602A or 'LS603A), refreshing is accomplished by dividing the safe refresh time into equal segments and refreshing one row in each segment. The segment time is programmed via the RC CYCLE STEAL input and will produce a low level on the READY output at the end of each segment period. This indicates to the CPU to suspend operations for one memory cycle for a row refresh. In effect it "steals" one memory cycle from the CPU. After the CPU recognizes the cycle-steal signal from the READY output, it must take both REF REQ pins high. These devices will then refresh one row and return control back to the CPU by taking READY high. The burst-mode timer is also provided to prevent exceeding the maximum allowable refresh time, and operates in the same manner as in the 'LS600A and 'LS601A. In applications where the burst-mode timer is not required, it can be disabled by connecting the RC Burst input to ground.

Pin numbers shown on logic notation are for DW, J or N packages.

(17) LATCHED RCO

RC BURST (19)

LATCHED (18)

Pin numbers shown on logic notation are for DW, J or N packages.

## PIN FUNCTION TABLE

| PIN       | PIN NAME              | FUNCTIONAL DESCRIPTION                                                                                                                                                                       |

|-----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | BUSY                  | Active output indicates to the CPU that a refresh cycle is in progress.                                                                                                                      |

| 16        | HOLD                  | Active output should be a priority interrupt to the CPU for emergency burst refresh.                                                                                                         |

| 15        | RAS                   | 3-state output row address strobe.                                                                                                                                                           |

| 11        | RC RAS HI             | Timing node for high-level portion of RAS. See Note 1.                                                                                                                                       |

| 12        | RC RAS LO             | Timing node for low-level portion of RAS. See Note 1.                                                                                                                                        |

| 2-8       | A0 thru A6            | 3-state output row address lines.                                                                                                                                                            |

| 9         | A7                    | MSB row address line for 'LS601A and 'LS603A (64K-bit memory controllers).                                                                                                                   |

| 9         | 4K/16K                | A high input level disables the A5 row address line for 'LS600A and 'LS602A. (The high-level input makes the count chain 5 bits long while the low-level makes the count chain 6 bits long.) |

| 17        | READY                 | Interrupt to CPU for cycle steal refresh ('LS602A and 'LS603A).                                                                                                                              |

| 17        | LATCHED RCO           | Normally high-level, will latch low upon RCO of counter ('LS600A or 'LS601A).                                                                                                                |

| 18        | RC CYCLE STEAL        | Timing node that controls the READY output ('LS602A and 'LS603A). See Note 1.                                                                                                                |

| 18        | RESET LATCHED<br>RCO  | Normally high-level, when pulsed low the LATCHED RCO output will be reset ('LS600A and 'LS601A).                                                                                             |

| 19        | RC BURST              | Timing node for burst refresh. See Note 1.                                                                                                                                                   |

| 13,<br>14 | REF REQ1,<br>REF REQ2 | High level on both pins starts and continues row refresh. Low on either pin inhibits refresh.                                                                                                |

| 20, 10    | V <sub>CC</sub> , GND | 5-V power supply and network ground pins.                                                                                                                                                    |

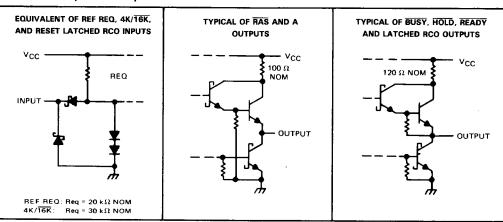

NOTE 1: All timing nodes require a resistor to  $V_{\hbox{\scriptsize CC}}$  and a capacitor to GND.

## schematics of inputs and outputs

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 2)     | 7 V   |

|--------------------------------------|-------|

| Input voltage                        | 7 V   |

| Off-state output voltage             | 5.5 V |

| Operating free-air temperature range |       |

| Storage temperature range65°C to 1   | 50°C  |

NOTE 2: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                                           |                            | MIN  | NOM | MAX   | UNIT |  |

|-------------------------------------------|----------------------------|------|-----|-------|------|--|

| Supply voltage, VCC                       |                            | 4.75 | 5   | 5.25  | V    |  |

| I Color I and a second I am               | A, RAS                     |      |     | - 2.6 | mA   |  |

| High-level output current, IOH            | All others                 |      |     | - 400 | μА   |  |

| 1 1 1 1                                   | A, RAS                     |      |     | 24    | T    |  |

| Low-level output current, IOL             | All others                 |      |     | 8     | ⊢ mA |  |

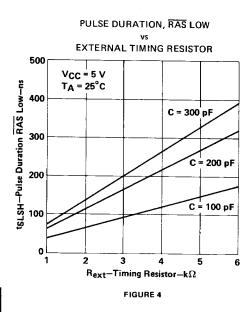

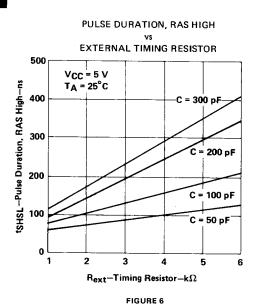

| Duration or RAS output pulse <sup>†</sup> | High, tSHSL                | 75   |     |       | ns   |  |

|                                           | Low, tSLSH                 | 75   |     |       |      |  |

| Duration of RESET LATCHED RCO pu          | ilse, t <sub>RHRL</sub>    | 35   |     |       | ns   |  |

| Duration of REF REQ pulse during CY       | CLE STEAL operation, tQHQL | 20   |     |       | ns   |  |

| Francis dining and and D                  | RC RAS LO, RC RAS HI       | 1    |     | 6     | kΩ   |  |

| External timing resistor, Rext            | RC BURST, RC CYCLE STEAL   | 1    |     | 1000  |      |  |

| Operating free-air temperature, TA        |                            | 0    |     | 70    | °C   |  |

<sup>†</sup>Maximum operating frequency for the address counter corresponds to its minimum period, which is the sum of tw(RAS-H) min and tw(RAS-L) min.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                                                            |                     | TEST CONDITIONS                                                                |                                                        | MIN          | TYP <sup>‡</sup> | MAX            | UNIT |

|-----------------|------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|--------------|------------------|----------------|------|

| VIH             | High-level input volta                                     | ge                  |                                                                                |                                                        | 2            |                  |                | ٧    |

| VIL             | Low-level input volta                                      | ge                  |                                                                                |                                                        |              |                  | 0.8            | V    |

| VIK             | Input clamp voltage                                        |                     | V <sub>CC</sub> = 4.75 V, I <sub>I</sub>                                       | = -1.8 mA                                              |              |                  | - 1.5          | V    |

| Vон             | High-level output voltage                                  | A,RAS               | V <sub>CC</sub> = 4.75 V,<br>V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = 0.8 V | I <sub>OH</sub> = -2.6 mA<br>I <sub>OH</sub> = -400 μA | 2.4          | 3.1              |                | v .  |

| Vol             | Low-level output                                           | A, RAS              | V <sub>IC</sub> = 4.75 V,<br>V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = 0.8 V | I <sub>OL</sub> = 12 mA<br>I <sub>OL</sub> = 24 mA     |              | 0.25<br>0.35     | 0.4<br>0.5     | v    |

| ·OL             | voltage                                                    | All Others          |                                                                                | I <sub>OL</sub> = 4 mA<br>I <sub>OL</sub> = 8 mA       |              | 0.25             | 0.4            |      |

| lozh            | Off-state output<br>current, high-level<br>voltage applied | A, RAS              | V <sub>CC</sub> = 5.25 V<br>REF REQ at<br>V <sub>IL</sub> = 0.8 V              | V <sub>O</sub> = 2.7 V                                 |              |                  | 20             | μА   |

| łozL            | Off-state output<br>current, low-level<br>voltage applied  | A, HAS              |                                                                                | V <sub>O</sub> = 0.4 V                                 |              |                  | - 20           | μΑ   |

| IJ              | Input current at maxi                                      | mum                 | V <sub>CC</sub> = 5.25 V,                                                      | V <sub>I</sub> = 7 V                                   |              |                  | 0.1            | mA   |

| Iн              | High-level input curre                                     | ent                 | $V_{CC} = 5.25 \text{ V},$                                                     | $V_1 = 2.7 \text{ V}$                                  |              |                  | 20             | μΑ   |

| I <sub>IL</sub> | Low-level input curre                                      | ent                 | $V_{CC} = 5.25 \text{ V},$                                                     | $V_1 = 0.4 V$                                          |              |                  | -0.4           | mA   |

| los             | Short-circuit<br>output current§                           | A,RAS<br>All others | V <sub>CC</sub> = 5.25 V                                                       |                                                        | - 30<br>- 20 |                  | - 130<br>- 100 | mA   |

| lcc             | Supply current                                             |                     | V <sub>CC</sub> = 5.25 V, R<br>REF REQ at 0 V                                  | C RAS LO and                                           |              | 50               | 85             | mA   |

$<sup>^{\</sup>ddagger}AII$  typical values are at VCC = 5 V, TA = 25 °C.

<sup>\$</sup>Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

# TYPES SN74LS600A THRU SN74LS603A MEMORY REFRESH CONTROLLERS

switching characteristics, VCC = 5 V, TA = 25 °C, see note 3

| PARAMETER                      | FROM (INPUT)  | TO (OUTPUT) | TEST CONDITIONS                                 | MIN TYP | MAX | UNIT |

|--------------------------------|---------------|-------------|-------------------------------------------------|---------|-----|------|

| <sup>t</sup> QHBL              | REF REQ1      | BUSY        | 0 45 5 0 0 0                                    | 30      | 45  | ns   |

| <sup>†</sup> SLBH              | RASI          | BUSY        | $C_L = 15 \text{ pF, } R_L = 2 \text{ k}\Omega$ | 245     | 300 | ns   |

| <sup>†</sup> QHSV              | REF REQ1      | RAS         | $C_L = 320 \text{ pF}, R_L = 667\Omega$         | 47      | 70  | ns   |

| <sup>t</sup> SHSZ <sup>†</sup> | RASI          | RAS         | $C_L = 5 pF, R_L = 667\Omega$                   | 245     | 300 | ns   |

| †QHAV                          | REF REQ1      | ADDRESS     | $C_L = 160 \text{ pF}, R_L = 667\Omega$         | 38      | 65  | ns   |

| tSHAZ†                         | RASt          | ADDRESS     | $C_L = 5 pF, R_L = 667\Omega$                   | 245     | 300 | ns   |

| tour                           | RESET LATCHED | LATCHED     |                                                 |         |     |      |

| <sup>t</sup> RHCL              | RCO1          | RCO         | $C_L = 15 pF, R_L = 2 k\Omega$                  | 37      | 55  | ns   |

| <sup>t</sup> SHYH              | RASt          | READY       | 7                                               | 64      | 85  | ns   |

| <sup>‡</sup> SLSH <sup>‡</sup> | RAS           | RAS         | G 200 F B 2070                                  | 210     |     | ns   |

| <sup>t</sup> SHSL <sup>†</sup> | RAS1          | RAS         | $C_L = 320 \text{ pF}, R_L = 667\Omega$         | 245     |     | ns   |

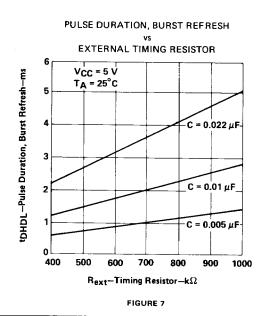

| tDHDL <sup>§</sup>             | HOLD1         | HOLD        | C - 15 - F P 210                                | 3.56    |     | ms   |

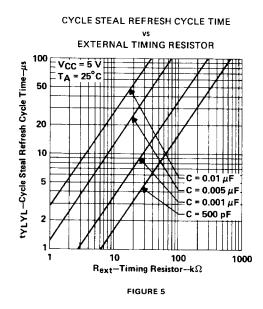

| tYLYL                          | READY         | READY       | $C_L = 15 \text{ pF}, R_L = 2 \text{ k}\Omega$  | 27      |     | μS   |

<sup>&</sup>lt;sup>†</sup> Depends on RC network at pin 11 (4 kΩ, 200 pF used for testing).

NOTE 3: See General Information Section for load circuits and voltage waveforms.

#### explanation of letter symbols

This data sheet uses a new type of letter symbol to describe time intervals. The format is:

#### tAR-CΓ

where:

subscripts A and C indicate the names of the signals for which changes of state or level or establishment of state or level constitute signal events assumed to occur first and last, respectively, that is, at the beginning and end of the time interval.

Subscripts B and D indicate the direction of the transitions and/or the final states or levels of the signals represented by A and C, respectively. One or two of the following is used:

H = high or transition to high

L = low or transition to low

V = a valid steady-state level

X = unknown, changing, or "don't care" level

Z = high-impedance (off) state.

The hyphen between the B and C subscripts is omitted when no confusion is likely to occur. For these letter symbols on this data sheet, the signal names are further abbreviated as follows:

| SIGNAL            | A or C    |

|-------------------|-----------|

| NAME              | SUBSCRIPT |

| BUSY              | В         |

| HOLD              | D         |

| RAS               | S         |

| A0 - A7           | Α         |

| READY             | Υ         |

| LATCHED RCO       | С         |

| RESET LATCHED RCO | R         |

| REF REQ           | Q         |

$<sup>^\</sup>ddagger$  Depends on RC network at pin 12 (4 kΩ, 200 pF used for testing).

<sup>§</sup> Depends on RC network at pin 19 (680 k $\Omega$ , 0.022  $\mu F$  used for testing).

Depends on RC network at pin 18 (10 kΩ, 0.01 μF used for testing).

During testing, an 'LSO4 is used to invert HOLD to provide the REF REQ input.

FIGURE 3 - BURST MODE REFRESH

## TYPICAL CHARACTERISTICS

Texas Instruments