# HM6168H-45,HM6168H-55, HM6168H-70,HM6168HP-45, HM6168HP-55,HM6168HP-70

4096-word×4-bit High Speed Static CMOS RAM

#### **FEATURES**

- High Speed: Fast Access Time 45/55/70 ns (max.)

- Single +5V Supply and High Density 20 Pin Package

- Low Power Standby and Low Power Operation;

100μW typ. (Standby), 200mW typ. (Operation)

- Completely Static Memory

No Clock or Timing Strobe Required

- Equal Access and Cycle Times

- Directly TTL Compatible All Inputs and Outputs

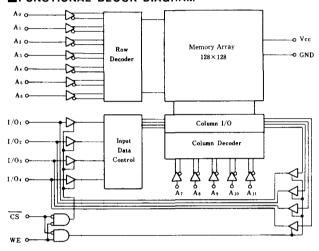

#### FUNCTIONAL BLOCK DIAGRAM

#### **■**ABSOLUTE MAXIMUM RATINGS

| ltem                               | Symbol | Rating                   | Unit |

|------------------------------------|--------|--------------------------|------|

| Voltage on Any Pin Relative to GND | VIN    | $-3.5^{\circ}$ to $+7.0$ | v    |

| Power Dissipation                  | Рτ     | 1.0                      | w    |

| Operating Temperature              | T.pr   | 0 to +70                 | °C   |

| Storage Temperature (Ceramic)      | Tete   | -65 to +150              | .c   |

| Storage Temperature (Plastic)      | T,te   | -55 to +125              | °C   |

| Temperature under Bias             | T      | -10 to +85               | ·c   |

<sup>\*</sup> Pulse Width 20ns, DC = -0.5V

#### **■PIN ARRANGEMENT**

(Top View)

#### **TRUTH TABLE**

| CS | WE | Mode         | V <sub>CC</sub> Current | I/O Pin | Reference Cycle  |

|----|----|--------------|-------------------------|---------|------------------|

| Н  | Х  | Not selected | $I_{SB}, I_{SB1}$       | High Z  |                  |

| L  | Н  | Read         | I <sub>CC</sub>         | Dout    | Read Cycle 1, 2  |

| L  | L  | Write        | I <sub>CC</sub>         | Din     | Write Cycle 1, 2 |

### ■ RECOMMENDED DC OPERATING CONDITIONS ( $Ta=0 \text{ to } + 70^{\circ}\text{C}$ )

| Item           | Symbol          | min   | typ | max | Unit |

|----------------|-----------------|-------|-----|-----|------|

| Supply Voltage | Vcc             | 4.5   | 5.0 | 5.5 | v    |

|                | GND             | 0     | 0   | 0   | v    |

| Input Voltage  | V <sub>IH</sub> | 2.2   | _   | 6.0 | v    |

|                | $V_{IL}$        | -0.5* | _   | 0.8 | v    |

<sup>\* -3.0</sup>V (Pulse width 20ns)

### ■ DC AND OPERATING CHARACTERISTICS ( $V_{CC}$ =5V ±10%, GND=0V, $T_a$ =0 to + 70°C)

| Item                            | Symbol             | Test Conditions                                                                                                | min | typ  | max      | Unit       |

|---------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|-----|------|----------|------------|

| Imput Leakage Current           | \I <sub>LI</sub> \ | $V_{CC}$ =5.5V, $V_{in}$ =GND to $V_{CC}$                                                                      | -   | -    | 2.0      | μА         |

| Output Leakage Current          | IILO I             | $\overline{\text{CS}} = V_{IH}, V_{I/O} = \text{GND to } V_{CC}$                                               | -   | -    | 2.0      | μА         |

| Operating Power Supply Current  | I <sub>CC</sub>    | $CS=V_{IL}, I_{I/O}=0$ mA                                                                                      | -   | 40   | 90       | mA         |

| Standby Power Supply Current    | I <sub>SB</sub>    | $\overline{\text{CS}} = V_{IH}$                                                                                | _   | 15   | 25       | mA         |

| Standby Power Supply Current(1) | I <sub>SB1</sub>   | $\overline{\text{CS}} = V_{CC} - 0.2 \text{V}, V_{IN} \leq 0.2 \text{V or } V_{IN} \geq V_{CC} - 0.2 \text{V}$ | -   | 0.02 | 2.0      | m <b>A</b> |

| Output Low Voltage              | VOL                | I <sub>OL</sub> = 8mA                                                                                          | -   | _    | 0.4      | v          |

| Output High Voltage             | V <sub>OH</sub>    | I <sub>OH</sub> = -4mA                                                                                         | 2.4 | _    | <b> </b> | v          |

Note: Typical limits are at  $V_{CC}$ =5.0V,  $T_a$ =25°C and specified loading.

### ■ CAPACITANCE $(T_a = 25^{\circ}C, f = 1MHz)$

| Item                     | Symbol    | Test Conditions            | min | max | Unit |

|--------------------------|-----------|----------------------------|-----|-----|------|

| Input Capacitance        | Cin       | <i>V</i> <sub>IN</sub> =0V | -   | 6   | pF   |

| Input/Output Capacitance | $C_{I/O}$ | $V_{I/O} = 0V$             | _   | 8   | pF   |

#### ■ AC CHARACTERISTICS ( $V_{CC}$ =5V ±10%, $T_a$ =0 to + 70°C, unless otherwise noted.)

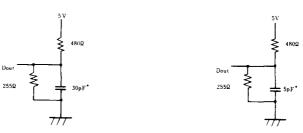

#### AC TEST CONDITION

Input pulse levels; GND to 3.0V

Input rise and fall times: 5ns

Input and Output timing reference levels: 1.5V

Output load: See Figure

Output Load (A)

\* Including scope and jig.

Output Load (B) (for  $t_{HZ}$ ,  $t_{LZ}$ ,  $t_{WZ}$ ,  $t_{OW}$ )

#### • READ CYCLE

| Item                                  | Symbol          | HM6168H/P-45 |     | HM6168H/P-55 |     | HM6168H/P-70 |     | 1    |

|---------------------------------------|-----------------|--------------|-----|--------------|-----|--------------|-----|------|

|                                       |                 | min          | max | min          | max | min          | max | Unit |

| Read Cycle Time                       | tRC             | 45           | _   | 55           | _   | 70           | -   | ns   |

| Address Access Time                   | tAA             | -            | 45  | _            | 55  | -            | 70  | ns   |

| Chip Select Access Time               | tACS            | _            | 45  |              | 55  | _            | 70  | ns   |

| Output Hold from Address Change       | t <sub>OH</sub> | 5            | _   | 5            | -   | 5            | -   | ns   |

| Chip Selection to Output in Low Z*    | $t_{LZ}$        | 20           |     | 20           | _   | 20           | -   | ns   |

| Chip Deselection to Output in High Z* | tHZ             | 0            | 20  | 0            | 20  | 0            | 20  | ns   |

| Chip Selection to Power Up Time       | tPU             | 0            | _   | 0            | _   | 0            | -   | ns   |

| Chip Deselection to Power Down Time   | $t_{PD}$        | -            | 30  | -            | 30  | -            | 30  | ns   |

<sup>\*</sup> Transition is measured ±500mV for high impedance voltage with Load (B). This parameter is sampled and not 100% tested.

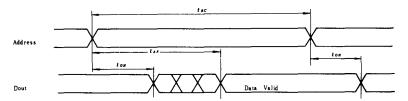

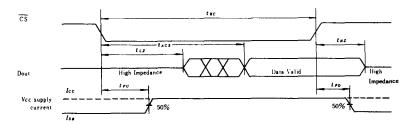

# • TIMING WAVEFORM OF READ CYCLE NO. 1(1), (2)

## • TIMING WAVEFORM OF READ CYCLE NO. 2(1), (3)

Notes) 1. WE is High for Read Cycle.

2. Device is continuously selected,  $\overline{CS} = V_{IL}$ .

3. Address Valid prior to or coincident with CS transition Low.

#### WRITE CYCLE

| Item                               | Symbol          | HM6168H/P-45 |     | HM6168H/P-55 |     | HM6168H/P-70 |     | 77.14 |

|------------------------------------|-----------------|--------------|-----|--------------|-----|--------------|-----|-------|

|                                    |                 | min          | max | min          | max | min          | max | Unit  |

| Write Cycle Time                   | twc             | 45           | -   | 55           | -   | 70           | _   | ns    |

| Chip Selection to End of Write     | tcw             | 40           | _   | 50           | -   | 60           | _   | ns    |

| Address Valid to End of Write      | tAW             | 40           | -   | 50           | -   | 60           | _   | ns    |

| Address Setup Time                 | t <sub>AS</sub> | 0            | 1 - | 0            | -   | 0            | -   | ns    |

| Write Pulse Width                  | t <sub>WP</sub> | 35           | -   | 45           | -   | 55           | -   | ns    |

| Write Recovery Time                | twR             | 0            | -   | 0            | -   | 0            | -   | ns    |

| Data Valid to End of Write         | t <sub>DW</sub> | 20           | -   | 25           | -   | 30           | _   | ns    |

| Data Hold Time                     | t <sub>DH</sub> | 0            | -   | 0            | -   | 0            |     | ns    |

| Write Enabled to Output in High Z* | twz             | 0            | 15  | 0            | 20  | 0            | 25  | ns    |

| Output Active from End of Write*   | tow             | 0            | -   | 0            | -   | 0            | -   | ns    |

<sup>\*</sup> Thansition is measured ±500mV from high impedance voltage with Load (B). This parameter is sampled and not 100% tested,

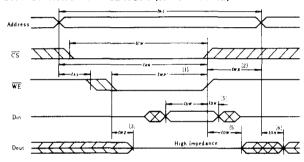

### • TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE Controlled)

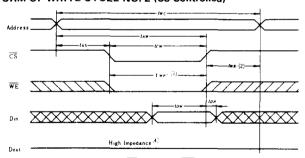

#### TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CS Controlled)

- Notes) 1. A write occurs during the overlap of <u>a low  $\overline{CS}$ </u> and a low  $\overline{WE}$ ,  $(t_{WP})$ 2.  $t_{WR}$  is measured from the earlier of  $\overline{CS}$  or  $\overline{WE}$  going high to the end of write cycle.

3. During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must

- not be applied.

4. If the CS low transition occurs simultaneously with the WE low transition or after the WE transition, the output buffer buffers remain in a high impedance state.

- 5. If  $\overline{\text{CS}}$  is low during this period, I/O pins are in the output state. Then the data input signals of opposite phase to

- the outputs must not be applied to them.

6. Dout is the same phase of Write data of this write cycle.