OCTOBER 1976-REVISED DECEMBER 1983

- Sink-Current Capability of 'LS295A

- Schottky-Diode-Clamped Transistors

- Low Power Dissipation . . . 80 mW Typical (Enabled)

- Applications:

N-Bit Serial-To-Parallel Converter N-Bit Parallel-To-Serial Converter N-Bit Storage Register

#### description

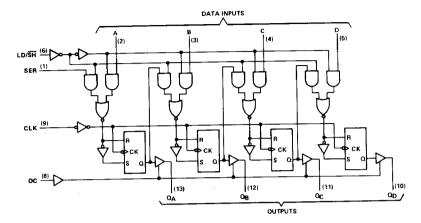

These 4-bit registers feature parallel inputs, parallel outputs, and clock (CLK), serial (SER), mode (LD/SH). and outputs control (OC) inputs. The registers have three modes of operation:

Parallel (broadside) load Shift right (the direction QA toward QD) Shift left (the direction QD toward QA)

Parallel loading is accomplished by applying the four bits of data and taking the mode control input high. The data is loaded into the associated flip-flops and appears at the outputs after the high-to-low transition of the clock input. During parallel loading, the entry of serial data is inhibited.

Shift right is accomplished when the mode control is low; shift left is accomplished when the mode control is high by connecting the output of each flip-flop to the parallel input of the previous flip-flop (QD to input C, etc.) and serial data is entered at input D.

When the output control is high, the normal logic levels of the four outputs are available for driving the loads or bus lines. The outputs are disabled independently from the level of the clock by a low logic level at the output control input. The outputs then present a high impedance and neither load nor drive the bus line: however, sequential operation of the registers is not affected.

The SN54LS295B is characterized for operation over the full military temperature range of -55°C to 125°C; the SN74LS295B is characterized for operation from 0°C to 70°C.

SN54LS295B ... J OR W PACKAGE SN74LS295B . . . D, J OR N PACKAGE (TOP VIEW)

SN54LS295B . . . FK PACKAGE SN74LS295B ... FN PACKAGE (TOP VIEW)

NC - No internal connection

Pin numbers shown on logic notation are for D, J or N packages.

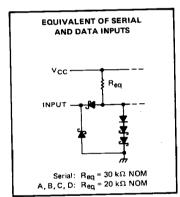

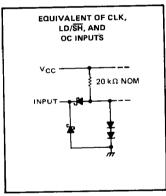

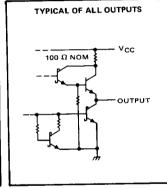

### schematics of inputs and outputs

3

TTL DEVICES

| INPUTS |     |     |          |          |           | OUTPUTS |                 |                     |              |                 |  |

|--------|-----|-----|----------|----------|-----------|---------|-----------------|---------------------|--------------|-----------------|--|

| LD/SH  | CLK | SER | PARALLEL |          |           |         |                 |                     |              |                 |  |

|        |     |     | Α        | В        | С         | Ð       | QA              | αв                  | $\sigma^{C}$ | αD              |  |

| н      | н   | ×   | X        | х        | Х         | ×       | Q <sub>A0</sub> | α <sub>B0</sub>     | QC0          | Ω <sub>D0</sub> |  |

| н      | +   | ×   | а        | ь        | С         | d       | а               | b                   | С            | d               |  |

| Н      | . ↓ | ×   | QB+      | $q_{Ct}$ | $a_{D}$ t | d       | Q <sub>Bn</sub> | $\alpha_{Cn}$       | $Q_{Dn}$     | d               |  |

| L      | н   | ×   | x        | X        | Х         | х       | Q <sub>A0</sub> | $oldsymbol{o}_{B0}$ | $a_{co}$     | $a_{D0}$        |  |

| L      | 1   | н   | x        | X        | Х         | х       | н               | $Q_{An}$            | $Q_{Bn}$     | $\alpha_{Cn}$   |  |

| L      | 1   | L   | X        | Х        | х         | X       | L               | $Q_{An}$            | $Q_{Bn}$     | $Q_{Cn}$        |  |

When the output control is low, the outputs are disabled to the high-impedance state; however, sequential operation of the registers is not affected.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| . 7 V     |

|-----------|

| . 7 V     |

| to 125°C  |

| C to 70°C |

| to 150°C  |

|           |

#### NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                 |                                                 |            | Sr   | SN54LS295B |            |      | SN74LS295B |       |      |

|-----------------|-------------------------------------------------|------------|------|------------|------------|------|------------|-------|------|

|                 |                                                 |            | MIN  | NOM        | MAX        | MIN  | NOM        | MAX   | UNIT |

| Vcc             | Supply voltage                                  |            | 4.5  | 5          | 5.5        | 4.75 | 5          | 5.25  | V    |

| loн             | High-level output current                       |            |      |            | <b>– 1</b> |      | -          | - 2.6 | mA   |

| OL              | Low-level output current                        |            |      |            | 12         |      |            | 24    | mA   |

| fclock          | Clock frequency                                 |            | ō    |            | 30         | 0    |            | 30    | MHz  |

| tw(clock)       | Width of clock pulse                            |            | 16   |            |            | 16   |            |       | ns   |

| t <sub>su</sub> | Setup time, high-level or low-level data        |            | 20   |            |            | 20   |            |       | ns   |

| t <sub>su</sub> | Setup time, LD/SH to CLK                        | high-level | 25   |            |            | 25   |            |       |      |

|                 | Setup time, ED/SH to CER                        | low-level  | 30   |            |            | 30   |            |       | ns   |

| th              | Hold time, high-level or low-level data         |            | 5    |            |            | 5    |            |       | ns   |

| th              | Hold time, high-level or low-level LD/SH to CLK |            | 0    |            |            | 0    |            |       | ns   |

| TA              | Operating free-air temperature                  |            | - 55 |            | 125        | 0    |            | 70    | °c   |

<sup>†</sup>Shifting left requires external connection of Q<sub>B</sub> to A, Q<sub>C</sub> to B, and Q<sub>D</sub> to C. Serial data is entered at input D.

H = high level (steady state), L = low level (steady state), X = irrelevant (any input, including transitions) $\downarrow = transition from high to low level$ .

a, b, c, d = the level of steady-state input at inputs A, B, C, or D, respectively.

$Q_{AO}$ ,  $Q_{BO}$ ,  $Q_{CO}$ ,  $Q_{DO}$  = the level of  $Q_{A}$ ,  $Q_{B}$ ,  $Q_{C}$ , or  $Q_{D}$ , respectively, before the indicated steady-state input conditions were established.  $Q_{AO}$ ,  $Q_{BO}$ ,  $Q_{CO}$ ,  $Q_{DO}$  = the level of  $Q_{AO}$ ,  $Q_{BO}$ ,  $Q_{CO}$ , or  $Q_{DO}$ , respectively, before the most-recent  $\downarrow$  transition of the clock.

### TYPES SN54LS295B, SN74LS295B 4-BIT RIGHT-SHIFT LEFT-SHIFT REGISTERS WITH 3-STATE OUTPUTS

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                                                         |                                                                  |                                                 |                         | SN54LS295B |      |      | SN74LS295B |      |                 | UNIT         |

|-----------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------|-------------------------|------------|------|------|------------|------|-----------------|--------------|

| PARAMETER |                                                         | TEST CONDITIONS <sup>†</sup>                                     |                                                 |                         | MIN        | ТҮР‡ | MAX  | MIN        | TYP‡ | MAX             | UNI          |

| VIH       | High-level input voltage                                |                                                                  |                                                 |                         | 2          |      |      | 2          |      |                 | V            |

|           | Low-level input voltage                                 |                                                                  |                                                 |                         |            |      | 0.7  | <u> </u>   |      | 0.8             | V            |

| - 16-     | Input clamp voltage                                     | V <sub>CC</sub> = MIN,                                           | I <sub>I</sub> = -18 mA                         |                         |            |      | -1.5 | <u> </u>   |      | -1.5            | V            |

|           | High-level output voltage                               | V <sub>CC</sub> = MIN,<br>V <sub>II</sub> = V <sub>IL</sub> max, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = MAX |                         | 2.4        | 3.4  |      | 2.4        | 3.1  |                 | V            |

|           |                                                         | V <sub>CC</sub> = MIN,                                           | V <sub>1H</sub> = 2 V,                          | OL = 12 mA              |            | 0.25 | 0.4  |            | 0.25 | 0.4             | $\Gamma_{v}$ |

| $v_{OL}$  | Low-level output voltage                                | VIL = VIL max                                                    | ***                                             | I <sub>OL</sub> = 24 mA |            |      |      |            | 0.35 | 0.5             | Ľ            |

| 1         | Off-state output current,<br>high-level voltage applied | V <sub>CC</sub> = MAX,<br>V <sub>O</sub> = 2.7 V                 | VIL = VIL max,                                  |                         |            |      | 20   |            |      | 20              | μ.           |

|           | Off-state output current,                               | V <sub>CC</sub> = MAX,<br>V <sub>O</sub> = 0.4 V                 | V <sub>1H</sub> = 2 V,                          |                         |            |      | -20  |            |      | <del>-</del> 20 | μ,           |

| կ         | Input current at maximum input voltage                  | VCC = MAX,                                                       | V <sub>1</sub> = 7 V                            |                         |            |      | 0.1  |            |      | 0.1             | <u> </u>     |

| ΊΗ        | High-level input current                                | V <sub>CC</sub> = MAX,                                           | V <sub>1</sub> = 2.7 V                          |                         | l          |      | 20   |            |      | 20              |              |

| 11L       | Low-level input current                                 | V <sub>CC</sub> = MAX,                                           | V <sub>I</sub> = 0.4 V                          |                         |            |      | -0.4 | +          |      | -0.4            | +-           |

| los       | Short-circuit output current§                           | V <sub>CC</sub> = MAX                                            |                                                 |                         | -30        |      | -130 | -30        |      | -130            | _            |

| -03_      | Supply current                                          | V <sub>CC</sub> = MAX,                                           | See Note 2                                      | Condition A             |            | 20   | 29   |            | 20   | 29              | ⊢ m          |

| Icc       |                                                         |                                                                  |                                                 | Condition B             | I          | 22   | 33   | <u> </u>   | 22   | 33              | _            |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

- A. Output control at 4.5 V and a momentary 3 V, then ground, applied to clock input.

- B. Output control and clock input grounded.

# switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 C, R<sub>L</sub> = 667 $\Omega$

| PARAMETER                                           | TEST CONDITIONS         | MIN | TYP | MAX | UNI |

|-----------------------------------------------------|-------------------------|-----|-----|-----|-----|

|                                                     |                         | 30  | 45  |     | MHz |

| nax Maximum clock frequency                         |                         |     | 14  | 20  | ns  |

| LH Propagation delay time, low-to-high-level output | C <sub>1</sub> = 45 pF, |     |     |     |     |

| HL Propagation delay time, high-to-low-level output | See Note 3              |     | 19  | 30  | ns  |

| PZH Output enable time to high level                |                         |     | 18  | 26  | ns  |

| ZL Output enable time to low level                  |                         | ļ   | 20  | 30  | ns  |

| HZ Output disable time from high level              | C <sub>L</sub> = 5 pF,  | L   | 13  | 20  | ns  |

| PLZ Output disable time from low level              | See Note 3              |     | 13  | 20  | ns  |

NOTE 3: See General Information Section for load circuits and voltage waveforms.

$<sup>^{\</sup>ddagger}$ All typical values are at  $V_{CC}$  = 5 V,  $T_{A}$  = 25°C.

Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

NOTE 2: ICC is measured with the outputs open, the serial input and mode control at 4.5 V, and the data inputs grounded under the following conditions: