# **Inverting Regulator - Buck, Boost, Switching**

## 1.5 A

# MC34063A, MC33063A, SC34063A, SC33063A, NCV33063A

The MC34063A Series is a monolithic control circuit containing the primary functions required for DC-to-DC converters. These devices consist of an internal temperature compensated reference, comparator, controlled duty cycle oscillator with an active current limit circuit, driver and high current output switch. This series was specifically designed to be incorporated in Step-Down and Step-Up and Voltage-Inverting applications with a minimum number of external components. Refer to Application Notes AN920A/D and AN954/D for additional design information.

#### **Features**

- Operation from 3.0 V to 40 V Input

- · Low Standby Current

- Current Limiting

- Output Switch Current to 1.5 A

- Output Voltage Adjustable

- Frequency Operation to 100 kHz

- Precision 2% Reference

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

This device contains 79 active transistors.

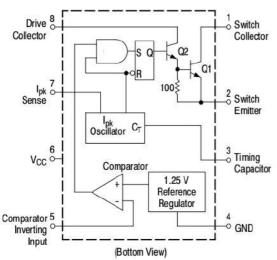

Figure 1. Representative Schematic Diagram

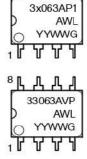

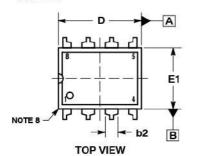

SOIC-8 D SUFFIX **CASE 751**

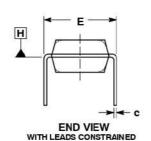

PDIP-8 P. P1 SUFFIX **CASE 626**

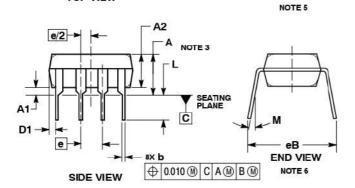

DFN8 CASE 488AF

= 3 or 4

= Assembly Location A

L, WL = Wafer Lot Y, YY = Year W. WW = Work Week = Pb-Free Package

## ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

Figure 2. Pin Connections

#### **MAXIMUM RATINGS**

| Rating                                             | Symbol                  | Value       | Unit |

|----------------------------------------------------|-------------------------|-------------|------|

| Power Supply Voltage                               | V <sub>CC</sub>         | 40          | Vdc  |

| Comparator Input Voltage Range                     | V <sub>IR</sub>         | -0.3 to +40 | Vdc  |

| Switch Collector Voltage                           | V <sub>C(switch)</sub>  | 40          | Vdc  |

| Switch Emitter Voltage (V <sub>Pin 1</sub> = 40 V) | V <sub>E(switch)</sub>  | 40          | Vdc  |

| Switch Collector to Emitter Voltage                | V <sub>CE(switch)</sub> | 40          | Vdc  |

| Driver Collector Voltage                           | V <sub>C(driver)</sub>  | 40          | Vdc  |

| Driver Collector Current (Note 1)                  | I <sub>C(driver)</sub>  | 100         | mA   |

| Switch Current                                     | Isw                     | 1.5         | А    |

| Power Dissipation and Thermal Characteristics      |                         |             |      |

| Plastic Package, P, P1 Suffix                      |                         |             |      |

| $T_A = 25^{\circ}C$                                | P <sub>D</sub>          | 1.25        | W    |

| Thermal Resistance                                 | R <sub>0JA</sub>        | 115         | °C/W |

| SOIC Package, D Suffix                             |                         |             |      |

| $T_A = 25^{\circ}C$                                | P <sub>D</sub>          | 625         | mW   |

| Thermal Resistance                                 | R <sub>θJA</sub>        | 160         | °C/W |

| Thermal Resistance                                 | R <sub>UC</sub>         | 45          | °C/W |

| DFN Package                                        |                         |             |      |

| $T_A = 25^{\circ}C$                                | P <sub>D</sub>          | 1.25        | mW   |

| Thermal Resistance                                 | R <sub>0</sub> JA       | 80          | °C/W |

| Operating Junction Temperature                     | Tj                      | +150        | °C   |

| Operating Ambient Temperature Range                | TA                      |             | °C   |

| MC34063A, SC34063A                                 |                         | 0 to +70    |      |

| MC33063AV, NCV33063A                               |                         | -40 to +125 |      |

| MC33063A, SC33063A                                 |                         | -40 to +85  | 1000 |

| Storage Temperature Range                          | T <sub>stg</sub>        | -65 to +150 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Maximum package power dissipation limits must be observed.

2. This device series contains ESD protection and exceeds the following tests: Human Body Model 4000 V per MIL–STD–883, Method 3015.

3. NCV prefix is for automotive and other applications requiring site and change control.

Machine Model Method 400 V.

$\textbf{ELECTRICAL CHARACTERISTICS} \ \ (V_{CC} = 5.0 \ V, T_{A} = T_{low} to \ T_{high} \ [Note 4], unless otherwise specified.)$

| Characteristics                                                                                                                        | Symbol                                | Min               | Тур        | Max           | Unit              |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|------------|---------------|-------------------|

| OSCILLATOR                                                                                                                             | ,,                                    |                   |            |               |                   |

| Frequency ( $V_{Pin 5} = 0 \text{ V}, C_T = 1.0 \text{ nF}, T_A = 25^{\circ}\text{C}$ )                                                | f <sub>osc</sub>                      | 24                | 33         | 42            | kHz               |

| Charge Current ( $V_{CC} = 5.0 \text{ V to } 40 \text{ V}, T_A = 25^{\circ}\text{C}$ )                                                 | l <sub>chg</sub>                      | 24                | 35         | 42            | μΑ                |

| Discharge Current ( $V_{CC} = 5.0 \text{ V}$ to 40 V, $T_A = 25^{\circ}\text{C}$ )                                                     | I <sub>dischg</sub>                   | 140               | 220        | 260           | μΑ                |

| Discharge to Charge Current Ratio (Pin 7 to V <sub>CC</sub> , T <sub>A</sub> = 25°C)                                                   | I <sub>dischg</sub> /I <sub>ohg</sub> | 5.2               | 6.5        | 7.5           | 352               |

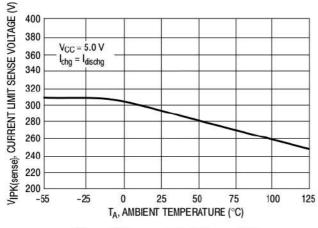

| Current Limit Sense Voltage (I <sub>chg</sub> = I <sub>dischg</sub> , T <sub>A</sub> = 25°C)                                           | V <sub>ipk(sense)</sub>               | 250               | 300        | 350           | mV                |

| OUTPUT SWITCH (Note 5)                                                                                                                 |                                       |                   | H          |               | 25                |

| Saturation Voltage, Darlington Connection (I <sub>SW</sub> = 1.0 A, Pins 1, 8 connected)                                               | V <sub>CE(sat)</sub>                  | -                 | 1.0        | 1.3           | ٧                 |

| Saturation Voltage (Note 6) (I <sub>SW</sub> = 1.0 A, R <sub>Pin 8</sub> = 82 $\Omega$ to V <sub>CC</sub> , Forced $\beta$ = 20)       | V <sub>CE(sat)</sub>                  | =                 | 0.45       | 0.7           | V                 |

| DC Current Gain ( $I_{SW} = 1.0 \text{ A}, V_{CE} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$ )                                         | h <sub>FE</sub>                       | 50                | 75         | (ES)          | 15 <del>5</del> 7 |

| Collector Off-State Current (V <sub>CE</sub> = 40 V)                                                                                   | I <sub>C(off)</sub>                   | 8 <del>55</del>   | 0.01       | 100           | μΑ                |

| COMPARATOR                                                                                                                             |                                       |                   |            |               |                   |

| Threshold Voltage  T <sub>A</sub> = 25°C  T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub>                                       | V <sub>th</sub>                       | 1.225<br>1.21     | 1.25       | 1.275<br>1.29 | ٧                 |

| Threshold Voltage Line Regulation (V <sub>CC</sub> = 3.0 V to 40 V)<br>MC33063, MC34063<br>MC33063V, NCV33063                          | Reg <sub>line</sub>                   | 5                 | 1.4<br>1.4 | 5.0<br>6.0    | mV                |

| Input Bias Current (V <sub>in</sub> = 0 V)                                                                                             | I <sub>IB</sub>                       | -                 | -20        | -400          | nA                |

| TOTAL DEVICE                                                                                                                           |                                       | 1000              |            |               |                   |

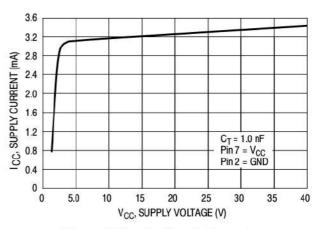

| Supply Current ( $V_{CC}$ = 5.0 V to 40 V, $C_T$ = 1.0 nF, Pin 7 = $V_{CC}$ , $V_{Pin 5} > V_{th}$ , Pin 2 = GND, remaining pins open) | lcc                                   | ( <del>5</del> 7) | 477        | 4.0           | mA                |

|                                                                                                                                        |                                       |                   |            |               |                   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics in the listed test conditions, diffess otherwise noted. Properformance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. T<sub>low</sub> = 0°C for MC34063, SC34063; -40°C for MC33063, SC33063, MC33063V, NCV33063

Thigh = +70°C for MC34063, SC34063; +85°C for MC33063, SC33063; +125°C for MC33063V, NCV33063

5. Low duty cycle pulse techniques are used during test by a direction temperature as close to antiboth size of the conditions are used to be a support of the conditions of the conditions are used to be a support of the conditions of the conditions are used to be a support of the conditions of the

IC output Forced  $\beta$  of output switch :  $\frac{100 \text{ dayat}}{\text{I}_{\text{C}} \text{ driver} - 7.0 \text{ mA*}} \ge 10$

<sup>6.</sup> If the output switch is driven into hard saturation (non-Darlington configuration) at low switch currents (≤ 300 mÅ) and high driver currents (≥ 30 mA), it may take up to 2.0 µs for it to come out of saturation. This condition will shorten the off time at frequencies ≥ 30 kHz, and is magnified at high temperatures. This condition does not occur with a Darlington configuration, since the output switch cannot saturate. If a non-Darlington configuration is used, the following output drive condition is recommended:

<sup>\*</sup>The 100  $\Omega$  resistor in the emitter of the driver device requires about 7.0 mA before the output switch conducts.

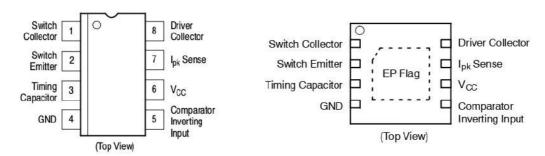

Ct, TIMING CAPACITOR CAPACITANCE (nF)

Figure 3. Oscillator Frequency

Figure 4. Timing Capacitor Waveform

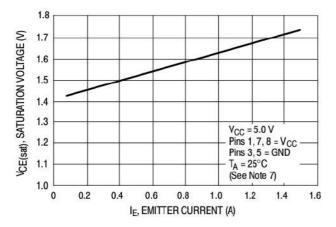

Figure 5. Emitter Follower Configuration Output Saturation Voltage versus Emitter Current

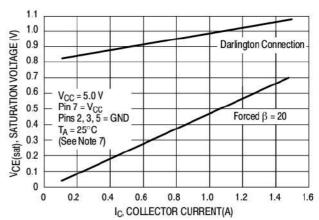

Figure 6. Common Emitter Configuration Output Switch Saturation Voltage versus Collector Current

Figure 7. Current Limit Sense Voltage versus Temperature

Figure 8. Standby Supply Current versus Supply Voltage

7. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient temperature as possible.

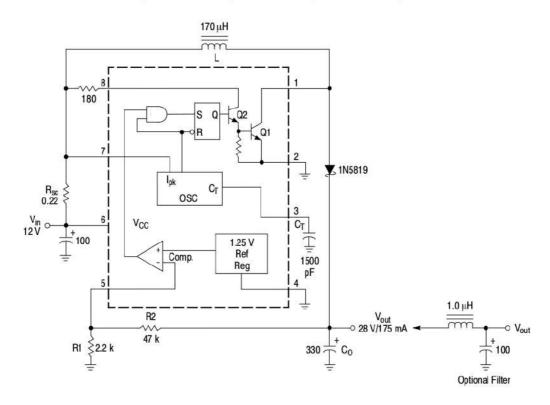

| Test                               | Conditions                                                        | Results         |

|------------------------------------|-------------------------------------------------------------------|-----------------|

| Line Regulation                    | V <sub>in</sub> = 8.0 V to 16 V, I <sub>O</sub> = 175 mA          | 30 mV = ±0.05%  |

| Load Regulation                    | $V_{in} = 12 \text{ V}, I_{O} = 75 \text{ mA to } 175 \text{ mA}$ | 10 mV = ±0.017% |

| Output Ripple                      | V <sub>in</sub> = 12 V, I <sub>O</sub> = 175 mA                   | 400 mVpp        |

| Efficiency                         | V <sub>in</sub> = 12 V, I <sub>O</sub> = 175 mA                   | 87.7%           |

| Output Ripple With Optional Filter | V <sub>in</sub> = 12 V, I <sub>O</sub> = 175 mA                   | 40 mVpp         |

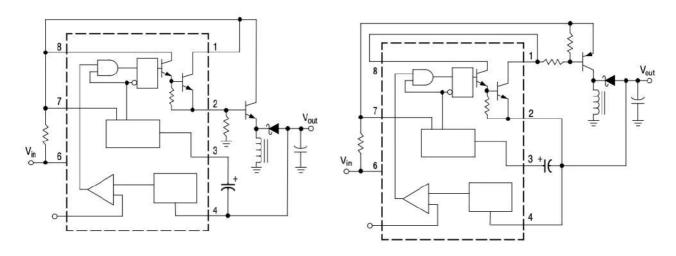

Figure 9. Step-Up Converter

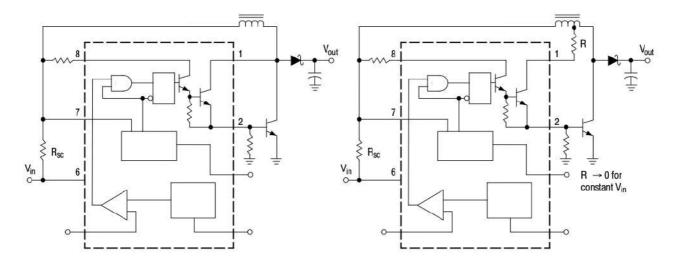

Figure 10. External Current Boost Connections for I<sub>C</sub> Peak Greater than 1.5 A

9a. External NPN Switch

9b. External NPN Saturated Switch (See Note 8)

8. If the output switch is driven into hard saturation (non-Darlington configuration) at low switch currents (≤300 mA) and high driver currents (≥30 mA), it may take up to 2.0 µs to come out of saturation. This condition will shorten the off time at frequencies ≥ 30 kHz, and is magnified at high temperatures. This condition does not occur with a Darlington configuration, since the output switch cannot saturate. If a non-Darlington configuration is used, the following output drive condition is recommended.

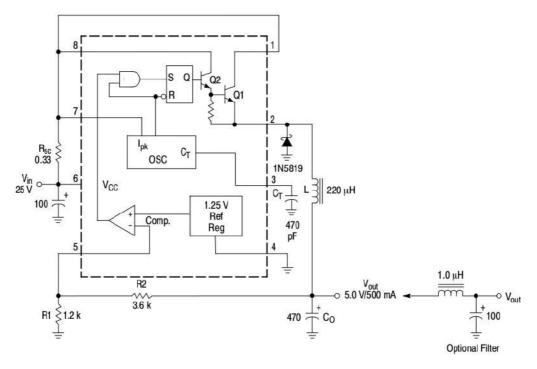

| Test                               | Conditions                                                        | Results         |  |

|------------------------------------|-------------------------------------------------------------------|-----------------|--|

| Line Regulation                    | V <sub>in</sub> = 15 V to 25 V, I <sub>O</sub> = 500 mA           | 12 mV = ±0.12%  |  |

| Load Regulation                    | $V_{in} = 25 \text{ V}, I_{O} = 50 \text{ mA to } 500 \text{ mA}$ | 3.0 mV = ±0.03% |  |

| Output Ripple                      | V <sub>in</sub> = 25 V, I <sub>O</sub> = 500 mA                   | 120 mVpp        |  |

| Short Circuit Current              | $V_{in}$ = 25 V, $R_L$ = 0.1 $\Omega$                             | 1.1 A           |  |

| Efficiency                         | V <sub>in</sub> = 25 V, I <sub>O</sub> = 500 mA                   | 83.7%           |  |

| Output Ripple With Optional Filter | V <sub>in</sub> = 25 V, I <sub>O</sub> = 500 mA                   | 40 mVpp         |  |

Figure 11. Step-Down Converter

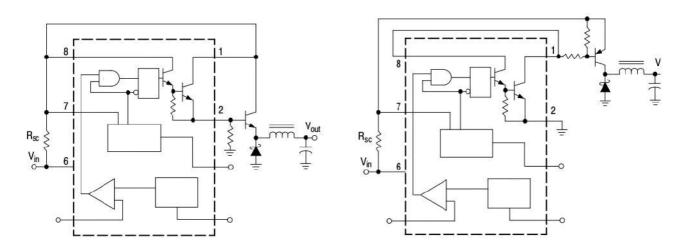

Figure 12. External Current Boost Connections for I<sub>C</sub> Peak Greater than 1.5 A

11a. External NPN Switch

11b. External PNP Saturated Switch

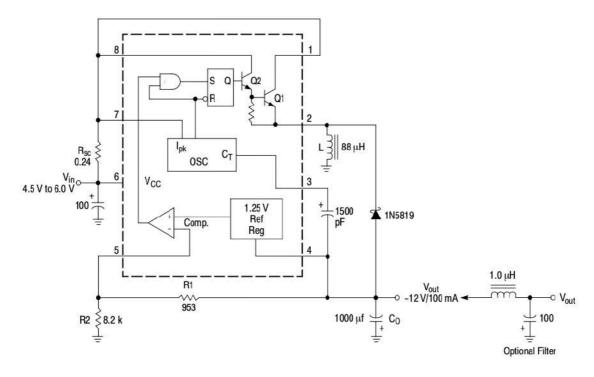

| Test                               | Conditions                                                          | Results                        |

|------------------------------------|---------------------------------------------------------------------|--------------------------------|

| Line Regulation                    | $V_{in} = 4.5 \text{ V to } 6.0 \text{ V, } I_{O} = 100 \text{ mA}$ | 3.0 mV = ±0.012%               |

| Load Regulation                    | $V_{in} = 5.0 \text{ V}, I_{O} = 10 \text{ mA to } 100 \text{ mA}$  | $0.022  \text{V} = \pm 0.09\%$ |

| Output Ripple                      | $V_{in} = 5.0 \text{ V}, I_{O} = 100 \text{ mA}$                    | 500 mVpp                       |

| Short Circuit Current              | $V_{in} = 5.0 \text{ V}, R_L = 0.1 \Omega$                          | 910 mA                         |

| Efficiency                         | $V_{in} = 5.0 \text{ V}, I_{O} = 100 \text{ mA}$                    | 62.2%                          |

| Output Ripple With Optional Filter | V <sub>in</sub> = 5.0 V, I <sub>O</sub> = 100 mA                    | 70 mVpp                        |

Figure 13. Voltage Inverting Converter

Figure 14. External Current Boost Connections for I<sub>C</sub> Peak Greater than 1.5 A 13b. External PNP Saturated Switch 13a. External NPN Switch

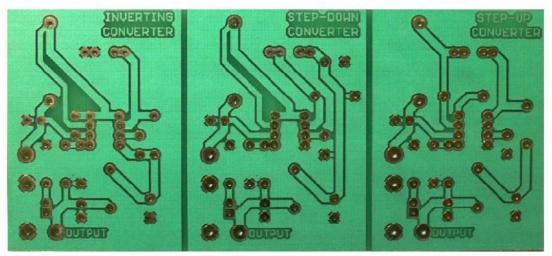

(Bottom Side)

(Top View, Component Side)

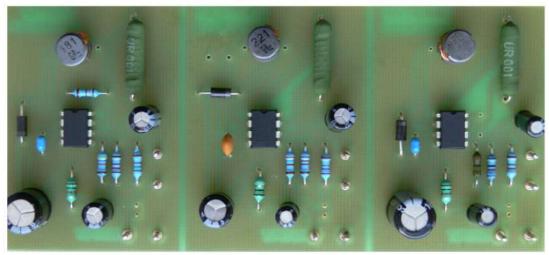

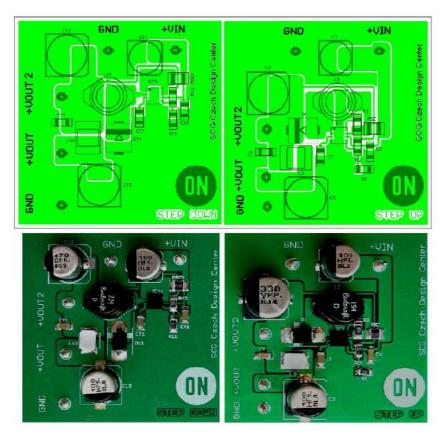

Figure 15. Printed Circuit Board and Component Layout (Circuits of Figures 9, 11, 13)

## INDUCTOR DATA

| Converter         | Inductance (μH) | Turns/Wire          |

|-------------------|-----------------|---------------------|

| Step-Up           | 170             | 38 Turns of #22 AWG |

| Step-Down         | 220             | 48 Turns of #22 AWG |

| Voltage-Inverting | 88              | 28 Turns of #22 AWG |

All inductors are wound on Magnetics Inc. 55117 toroidal core.

Figure 16. Printed Circuit Board for DFN Device

| Calculation                           | Step-Up                                                                                               | Step-Down                                                                                                                | Voltage-Inverting                                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| t <sub>on</sub> /t <sub>off</sub>     | $\frac{V_{out} + V_{F} - V_{in(min)}}{V_{in(min)} - V_{sat}}$                                         | Vout + V <sub>F</sub><br>Vin(min) - V <sub>sat</sub> - V <sub>out</sub>                                                  | $\frac{ V_{out}  + V_F}{V_{in} - V_{sat}}$                                        |

| (t <sub>on</sub> + t <sub>off</sub> ) | <u>1</u>                                                                                              | <u>1</u>                                                                                                                 | <u>1</u>                                                                          |

| t <sub>off</sub>                      | $\frac{t_{\text{on}} + t_{\text{off}}}{\frac{t_{\text{on}}}{t_{\text{off}}} + 1}$                     | $\frac{\frac{t_{OII} + t_{Off}}{t_{OII}}}{\frac{t_{OII}}{t_{Off}} + 1}$                                                  | $\frac{t_{\text{on}} + t_{\text{off}}}{\frac{t_{\text{on}}}{t_{\text{off}}} + 1}$ |

| t <sub>on</sub>                       | $(t_{on} + t_{off}) - t_{off}$                                                                        | (t <sub>on</sub> + t <sub>off</sub> ) - t <sub>off</sub>                                                                 | $(t_{on} + t_{off}) - t_{off}$                                                    |

| CT                                    | 4.0 x 10 <sup>-5</sup> t <sub>on</sub>                                                                | 4.0 x 10 <sup>-5</sup> t <sub>on</sub>                                                                                   | 4.0 x 10 <sup>-5</sup> t <sub>on</sub>                                            |

| I <sub>pk(switch)</sub>               | $2I_{out(max)}\left(\frac{t_{on}}{t_{off}} + 1\right)$                                                | <sup>2l</sup> out(max)                                                                                                   | $2I_{out(max)}\left(\frac{t_{on}}{t_{off}} + 1\right)$                            |

| R <sub>sc</sub>                       | 0.3/I <sub>pk(switch)</sub>                                                                           | 0.3/I <sub>pk(switch)</sub>                                                                                              | 0.3/l <sub>pk(switch)</sub>                                                       |

| L <sub>(min)</sub>                    | $\left(\frac{(V_{\text{in(min)}} - V_{\text{sat}})}{I_{\text{pk(switch)}}}\right) t_{\text{on(max)}}$ | $\left(\frac{(V_{\text{in(min)}} - V_{\text{sat}} - V_{\text{out}})}{I_{\text{pk(switch)}}}\right)^{t_{\text{on(max)}}}$ | $\left(\frac{(V_{in(min)} - V_{sat})}{I_{pk(switch)}}\right) t_{on(max)}$         |

| Со                                    | 9 Vripple (pp)                                                                                        | Ipk(switch) <sup>(t</sup> on + t <sub>off</sub> ) 8V <sub>ripple(pp)</sub>                                               | 9 Vripple(pp)                                                                     |

$V_{sat}$  = Saturation voltage of the output switch.

## The following power supply characteristics must be chosen:

V<sub>in</sub> - Nominal input voltage.

$V_{out}$  - Desired output voltage,  $|V_{out}| = 1.25 \left(1 + \frac{R2}{R1}\right)$

I<sub>out</sub> - Desired output current.

$f_{min}$  - Minimum desired output switching frequency at the selected values of  $V_{in}$  and  $I_{O}$ .

V<sub>ripple(pp)</sub> – Desired peak-to-peak output ripple voltage. In practice, the calculated capacitor value will need to be increased due to its equivalent series resistance and board layout. The ripple voltage should be kept to a low value since it will directly affect the line and load regulation.

NOTE: For further information refer to Application Note AN920A/D and AN954/D.

Figure 17. Design Formula Table

V<sub>F</sub> = Forward voltage drop of the output rectifier.

#### ORDERING INFORMATION

| Device          | Package             | Shipping <sup>†</sup>    |  |

|-----------------|---------------------|--------------------------|--|

| MC33063ADG      | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |  |

| MC33063ADR2G    | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |  |

| SC33063ADR2G    | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |  |

| MC33063AP1G     | PDIP-8<br>(Pb-Free) | 50 Units / Rail          |  |

| MC33063AVDG     | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |  |

| MC33063AVDR2G   | SOIC-8<br>(Pb-Free) | 1                        |  |

| NCV33063AVDR2G* | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |  |

| MC33063AVPG     | PDIP-8<br>(Pb-Free) | 50 Units / Rail          |  |

| MC34063ADG      | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |  |

| MC34063ADR2G    | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |  |

| SC34063ADR2G    | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |  |

| MC34063AP1G     | PDIP-8<br>(Pb-Free) | 50 Units / Rail          |  |

| SC34063AP1G     | PDIP-8<br>(Pb-Free) | 50 Units / Rail          |  |

| MC33063MNTXG    | DFN8<br>(Pb-Free)   | 4000 Units / Tape & Reel |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

<sup>\*</sup>NCV33063A: T<sub>low</sub> = -40°C, T<sub>high</sub> = +125°C. Guaranteed by design. NCV prefix is for automotive and other applications requiring site and change control.

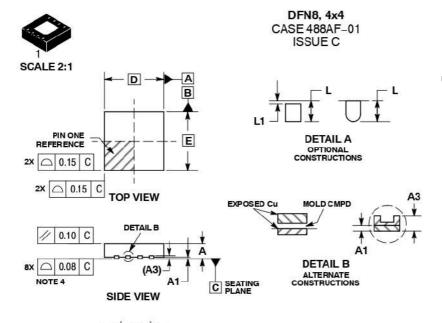

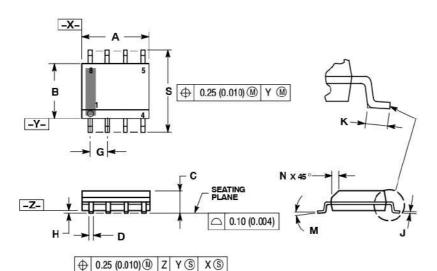

#### **MECHANICAL CASE OUTLINE**

- NOTES: 1. DIMENSIONS AND TOLERANCING PER

- DIMENSIONS AND TOLEHANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30MM FROM TERMINAL TIP. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

- DETAILS A AND B SHOW OPTIONAL CONSTRUCTIONS FOR TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| A3  | 0.20        | REF  |  |

| b   | 0.25 0.35   |      |  |

| D   | 4.00 BSC    |      |  |

| D2  | 1.91        | 2.21 |  |

| Е   | 4.00        | BSC  |  |

| E2  | 2.09        | 2.39 |  |

| е   | 0.80 BSC    |      |  |

| K   | 0.20        | 1    |  |

| L   | 0.30        | 0.50 |  |

| L1  |             | 0.15 |  |

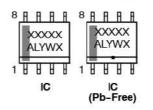

#### GENERIC MARKING DIAGRAM\*

= Specific Device Code XXXX

= Assembly Location A

L = Wafer Lot = Year

W = Work Week

= Pb-Free Package (Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " •",

may or may not be present.

#### D2 8x L DETAIL O Did D E2 ax h 0.10 CAB 0 0.05 C NOTE 3 **BOTTOM VIEW**

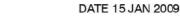

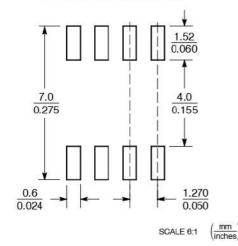

# SOLDERING FOOTPRINT\*

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON15232D     | Electronic versions are uncontrolled except when accessed diredly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED |             |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | DFN8, 4X4, 0.8P |                                                                                                                                             | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

PDIP-8 CASE 626-05 ISSUE P

**DATE 22 APR 2015**

STYLE 1:

PIN 1. AC IN

2. DC + IN

3. DC - IN

4. AC IN

5. GROUND

6. OUTPUT

7. AUXILIARY

8. V<sub>CC</sub>

#### NOTES

- IES DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION INCHES. DIMENSIONS A. A1 AND L. ARE MEASURED WITH THE PACKAGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3. DIMENSIONS D. D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE

- NOT TO EXCEED 0.10 INCH.

DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM

PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C.

DIMENSION OB IS MEASURED AT THE LEAD TIPS WITH THE

- DIMENSION BY IS MEASURED AT THE LEAD IT IS WITH THE LEADS UNCONSTRAINED.

DATUM PLANE IT IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY.

REPORT OF THE LEADS EXIT THE BODY.

REPORT OF THE LEADS EXIT THE BODY.

REPORT OF THE LEADS EXIT THE BODY.

REPORT OF THE LEADS EXIT THE BODY.

REPORT OF THE LEADS EXIT THE BODY.

REPORT OF THE LEADS EXIT THE LEAD IT IS WITH THE L

|     | INC   | HES   | MILLIN | IETERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   |       | 0.210 |        | 5.33   |

| A1  | 0.015 |       | 0.38   |        |

| A2  | 0.115 | 0.195 | 2.92   | 4.95   |

| b   | 0.014 | 0.022 | 0.35   | 0.56   |

| b2  | 0.060 | TYP   | 1.52   | TYP    |

| С   | 0.008 | 0.014 | 0.20   | 0.36   |

| D   | 0.355 | 0.400 | 9.02   | 10.16  |

| D1  | 0.005 |       | 0.13   |        |

| E   | 0.300 | 0.325 | 7.62   | 8.26   |

| E1  | 0.240 | 0.280 | 6.10   | 7.11   |

| е   | 0.100 | BSC   | 2.54   | BSC    |

| eВ  |       | 0.430 |        | 10.92  |

| L   | 0.115 | 0.150 | 2.92   | 3.81   |

| M   |       | 10°   |        | 10°    |

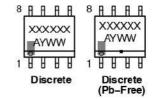

#### GENERIC MARKING DIAGRAM\*

XXXX = Specific Device Code = Assembly Location A

WL = Wafer Lot YY = Year ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " •", may or may not be present.

| DOCUMENT NUMBER: | 98ASB42420B | Electronic versions are uncontrolled except when accessed diredty from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | PDIP-8      |                                                                                                                                                                              | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

## **MECHANICAL CASE OUTLINE**

PACKAGE DIMENSIONS

#### SOIC-8 NB CASE 751-07 ISSUE AK

**DATE 16 FEB 2011**

#### NOTES

- TTES:

DIMENSIONING AND TOLERANCING PER

ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B DO NOT INCLUDE

MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006)

- PER SIDE

- DIMENSION DIDOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION. 751–01 THRU 751–06 ARE OBSOLETE NEW STANDARD IS 751–07.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |

| M   | 0 0         | 8 °  | 0 °       | 8 °   |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |

## SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

= Assembly Location

= Wafer Lot 1 = Year

= Work Week W

= Pb-Free Package

XXXXXX = Specific Device Code

= Assembly Location

= Year

WW = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### STYLES ON PAGE 2

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |      |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| DESCRIPTION:     | SOIC-8 NB   | PAGE 1                                                                                                                                                                              | OF 2 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

#### SOIC-8 NB CASE 751-07 ISSUE AK

## **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2:  PIN 1. COLLECTOR, DIE, #1  2. COLLECTOR, #1  3. COLLECTOR, #2  4. COLLECTOR, #2  5. BASE, #2  6. EMITTER, #2  7. BASE, #1  8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                            | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1                                      |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                                      | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. DRAIN                                                                                |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. DRAIN                                                                     | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                             | STYLE 15:  PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON 8. CATHODE, COMMON              | STYLE 16:  PIN 1. EMITTER, DIE #1  2. BASE, DIE #1  3. EMITTER, DIE #2  4. BASE, DIE #2  5. COLLECTOR, DIE #2  6. COLLECTOR, DIE #2  7. COLLECTOR, DIE #1  8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURGE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                         | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURGE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. DRAIN                                                                  |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1.   /O LINE 1 2.  COMMON CATHODE/VCC 3.  COMMON CATHODE/VCC 4.   /O LINE 3 5.  COMMON ANODE/GND 6.   /O LINE 4 7.   /O LINE 5 8.  COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 9. COLLECTOR/ANODE                                              |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/ott 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                           | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VEULK 7. VBULK 8. VIN                                                                                |

| STYLE 29: PIN 1. BASE DIE #1 2. EMITTER, #1 3. BASE #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                          | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1,DRAIN 2 6. SOURCE 1,DRAIN 2 7. SOURCE 1,DRAIN 2 8. GATE 1                                   |                                                                                                                                                     |                                                                                                                                                                                 |

|              |           | Electronic versions are uncontrolled except when accessed directly from the<br>Printed versions are uncontrolled except when stamped "CONTROLLED Co |             |

|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION: | SOIC-8 NB |                                                                                                                                                     | PAGE 2 OF 2 |

ON Semiconductor and IIII are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC doa "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of paterts, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="https://www.nsemi.com/site/pdf/Patent-Marking.pdf">www.nsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer applications by customer's technical experts. onsemi does not convey any license or any of its intellectual property rights nor the rights of others, onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buye

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910

onsemi Website: www.onsemi.com Phone: 011 421 33 790 2910 For additional information, please contact your local Sales Representative