# HD6303X, HD63A03X, **HD63B03X CMOS MPU** (Micro Processing Unit)

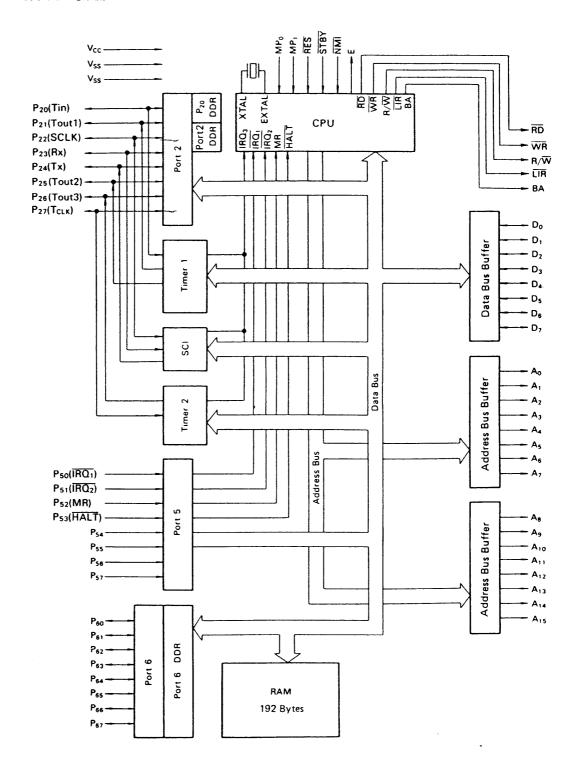

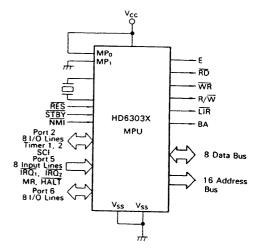

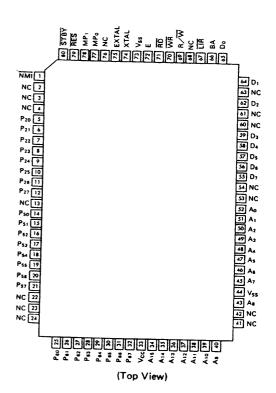

The HD6303X is a CMOS 8-bit micro processing unit (MPU) which includes a CPU compatible with the HD6301VI, 192 bytes of RAM, 24 parallel I/O pins, a Serial Communication Interface (SCI) and two timers on chip.

- **FEATURES**

- Instruction Set Compatible with the HD6301V1

- 192 Bytes of RAM

- 24 Parallel I/O Pins 16 I/O Pins-Port 2, 6 8 Input Pins-Port 5

- Darlington Transistor Drive (Port 2, 6)

- 16-Bit Programmable Timer Input Capture Register x 1 Free Running Counter x 1 Output Compare Register x 2 8-Bit Reloadable Timer

- External Event Counter Square Wave Generation

- Serial Communication Interface

- Memory Ready

- Error-Detection (Address Trap, Op-Code Trap)

- Interrupts . . . 3 External, 7 Internal

- Up to 65k Bytes Address Space

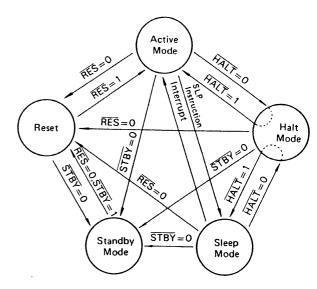

- Low Power Dissipation Mode Sleep Mode

- Standby Mode Minimum Instruction Execution Time -0.5μs (f = 2.0 MHz)

- Wide Range of Operation

$V_{cc} = 3 \sim 6V \text{ (f = 0.1 $\sim 0.5$ MHz)}.$  $V_{cc} = 5V\pm10\% \begin{cases} f = 0.1 \sim 1.0 \text{ MHz; HD6303X} \\ f = 0.1 \sim 1.5 \text{ MHz; HD63A03X} \\ f = 0.1 \sim 2.0 \text{ MHz; HD63B03X} \end{cases}$

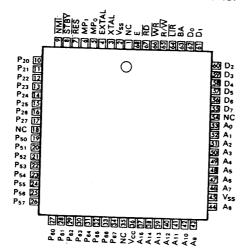

### ■ BLOCK DIAGRAM

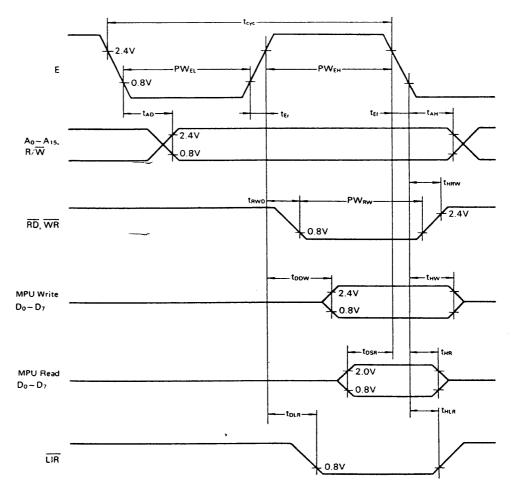

• AC CHARACTERISTICS ( $V_{CC}$  = 5.0V±10%,  $V_{SS}$  = 0V,  $T_a$  = 0  $\sim$  +70°C, unless otherwise noted.)

### **BUS TIMING**

|                          |            |                  | Test              | Н        | D6303> | (   | н        | 063A03   | X   | Н   | D63B03 | 3X  | Unit             |    |

|--------------------------|------------|------------------|-------------------|----------|--------|-----|----------|----------|-----|-----|--------|-----|------------------|----|

| Item                     |            | Symbol           | Condition         | min      | typ    | max | min      | typ      | max | min | typ    | max |                  |    |

| Cycle Time               |            | t <sub>cyc</sub> |                   | 1        | _      | 10  | 0.666    | _        | 10  | 0.5 |        | 10  | μs               |    |

| Enable Rise Time         |            | ter              |                   | _        | _      | 25  | -        | -        | 25  | -   |        | 25  | ns               |    |

| Enable Fall Time         |            | tef              |                   | -        | -      | 25  | _        | -        | 25  |     |        | 25  | ns               |    |

| Enable Pulse Width "Hi   | gh" Level* | PWEH             |                   | 450      | -      |     | 300      |          | -   | 220 | _      |     | ns               |    |

| Enable Pulse Width "Lo   | w" Level*_ | PWEL             |                   | 450      | -      | _   | 300      |          | _   | 220 | _      |     | ns               |    |

| Address, R/W Delay Tir   | ne*        | t <sub>AD</sub>  |                   | _        | _      | 250 | -        |          | 190 |     |        | 160 | ns               |    |

| Data Delay Time          | Write      | toow             |                   |          | -      | 200 |          | _        | 160 |     |        | 120 | ns               |    |

| Data Set-up Time         | Read       | tosa             | Fig. 1            | 80       |        | _   | 70       | _        | -   | 70  |        |     | ns               |    |

| Address, R/W Hold Tim    | ne*        | t <sub>AH</sub>  | Fig. 1            | 80       | -      | _   | 50       | -        | -   | 35  | _      |     | ns               |    |

| S . 11 11 T'             | Write*     | thw              |                   | 80       |        |     | 50       | -        |     | 40  |        |     | ns               |    |

| Data Hold Time           | Read       | tHR              |                   | 0        |        |     | 0        |          |     | 0   |        |     | ns               |    |

| RD, WR Pulse Width*      |            | PWRW             |                   | 450      | -      |     | 300      |          |     | 220 |        |     | ns               |    |

| RD, WR Delay Time        |            | t <sub>RWD</sub> |                   | <u> </u> | _      | 40  | <u> </u> |          | 40  | _   |        | 40  | ns               |    |

| RD, WR Hold Time         |            | t <sub>HRW</sub> |                   |          | _      | _   | 30       |          |     | 30  |        |     | 25               | ns |

| LIR Delay Time           |            | TOLR             |                   |          | _      | -   | 200      |          |     | 160 | _      |     | 120              | ns |

| LIR Hold Time            |            | tHLR             | ]                 | 10       |        |     | 10       | _        |     | 10  |        |     | ns               |    |

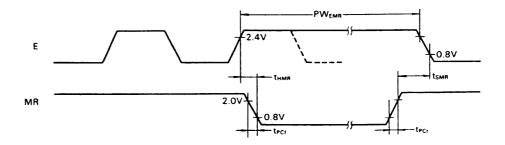

| MR Set-up Time*          |            | t <sub>SMR</sub> |                   | 400      |        | _   | 280      |          |     | 230 |        |     | ns               |    |

| MR Hold Time*            |            | tHMR             | Fig. 2            | _        |        | 90  |          | _        | 40  |     | _      | 0   | ns               |    |

| E Clock Pulse Width at   | MR         | PWEMR            |                   |          | _      | 9   |          | <u> </u> | 9   |     |        | 9   | μs               |    |

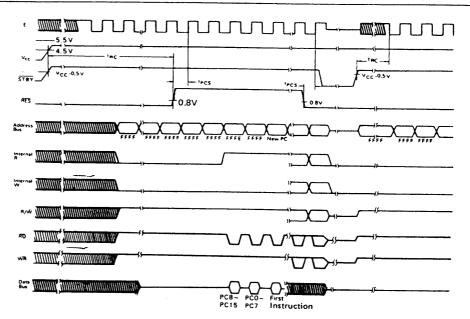

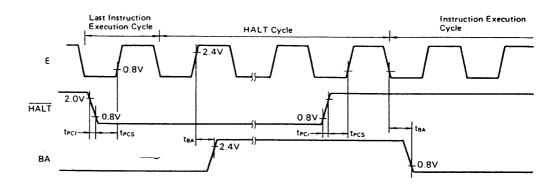

| Processor Control Set-L  | ıp Time    | t <sub>PCS</sub> | Fig. 3,<br>10, 11 | 200      | _      | _   | 200      |          | -   | 200 | _      |     | ns               |    |

| Processor Control Rise   | Time       | t <sub>PCr</sub> | 5:- 2.2           | -        | -      | 100 | _        |          | 100 | _   |        | 100 | ns               |    |

| Processor Control Fall   | Time       | t <sub>PCf</sub> | Fig. 2, 3         | _        | _      | 100 | _        |          | 100 |     |        | 100 | ns               |    |

| BA Delay Time            |            | t <sub>BA</sub>  | Fig. 3            | _        | _      | 250 | -        |          | 190 |     | _      | 160 | ns               |    |

| Oscillator Stabilization | Time       | t <sub>RC</sub>  | Fig. 11           | 20       | _      | _   | 20       | _        | _   | 20  | _      |     | ms               |    |

| Reset Pulse Width        |            | PWRST            |                   | 3        | -      | -   | 3        | T -      | -   | 3   |        |     | t <sub>cyc</sub> |    |

<sup>\*</sup> These timings change in approximate proportion to t<sub>CyC</sub>. The figures in this characteristics represent those when t<sub>CyC</sub> is minimum

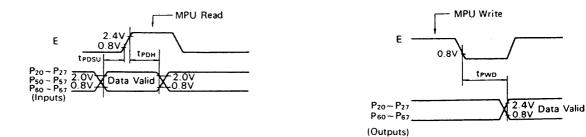

## PERIPHERAL PORT TIMING

|                                                              |                  |                   | Test      | Н   | D6303 | ×   | HE  | 063A03 | X   | Н   | D63B0 | 3X  | Unit |

|--------------------------------------------------------------|------------------|-------------------|-----------|-----|-------|-----|-----|--------|-----|-----|-------|-----|------|

| Ite                                                          | m                | Symbol            | Condition | min | typ   | max | min | typ    | max | min | typ   | max | J    |

| Peripheral Data<br>Set-up Time                               | Ports 2, 5, 6    | † <sub>PDSU</sub> | Fig. 5    | 200 |       | -   | 200 | _      | _   | 200 | -     | _   | ns   |

| Peripheral Data<br>Hold Time                                 | Ports 2, 5, 6    | t <sub>PDH</sub>  | Fig. 5    | 200 | -     | -   | 200 | -      | _   | 200 | -     | _   | ns   |

| Delay Time (Enal<br>Negative Transition<br>Peripheral Data V | on to Ports 2, 6 | t <sub>PWD</sub>  | Fig. 6    | _   | -     | 300 | -   | -      | 300 | -   | _     | 300 | ns   |

Figure 1 Bus Timing

Figure 2 Memory Ready and E Clock Timing

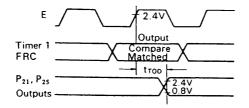

(a) Timer 1 Output Timing

(b) Timer 2 Output Timing

Figure 7 Timer Output Timing

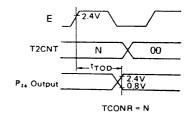

Figure 8 Timer 1.2, SCI Input Clock Timing

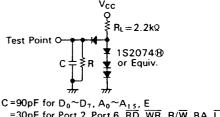

C = 90pF for  $D_0 \sim D_7$ ,  $A_0 \sim A_{15}$ , E = 30pF for Port 2, Port 6,  $\overline{RD}$ ,  $\overline{WR}$ ,  $R/\overline{W}$ , BA,  $\overline{LIR}$  $R=12k\Omega$

Figure 9 Bus Timing Test Loads (TTL Load)

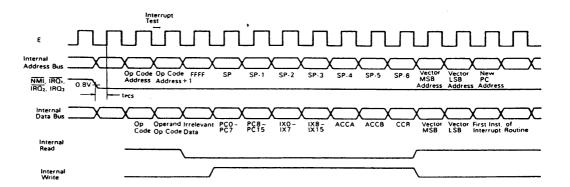

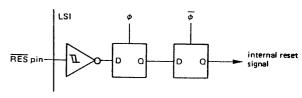

Figure 10 Interrupt Sequence

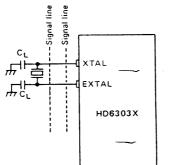

becomes normal oscillation after power on (max. 20ms). During this transient time, the MPU and I/O pins are undefined. Please be aware of this for system designing.

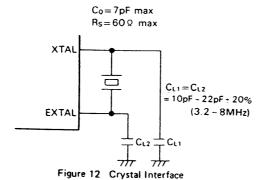

### • Enable (E)

This pin provides a TTL-compatible system clock to external circuits. Its frequency is one fourth that of the crystal oscillator or external clock. This pin can drive one TTL load and 90pF capacitance.

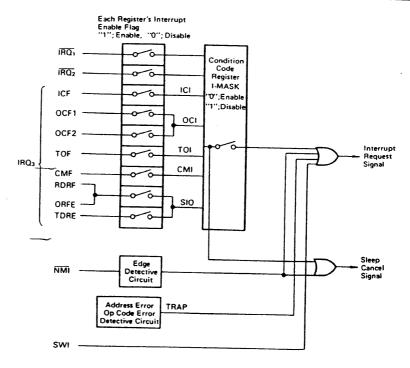

### Non-Maskable Interrupt (NMI)

When the falling edge of the input signal is detected at this pin, the CPU begins non-maskable interrupt sequence internally. As well as the IRQ mentioned below, the instruction being executed at NMI signal detection will proceed to its completion. The interrupt mask bit of the condition code register doesn't affect non-maskable interrupt at all.

When starting the acknowledge to the NMI, the contents of the program counter, index register, accumulators and condition code register will be saved onto the stack. Upon completion of this sequence, a vector is fetched from \$FFFC and \$FFFD to transfer their contents into the program counter and branch to the non-maskable interrupt service routine.

(Note) After reset start, the stack pointer should be initialized on an appropriate memory area and then the falling edge

should be input to NMI pin.

### Interrupt Request (IRQ₁, IRQ₂)

These are level-sensitive pins which request an internal interrupt sequence to the CPU. At interrupt request, the CPU will complete the current instruction before its request acknowledgement. Unless the interrupt mask in the condition code register is set, the CPU starts an interrupt sequence; if set, the interrupt request will be ignored. When the sequence starts, the contents of the program counter, index register, accumulators and condition code register will be saved onto the stack, then the CPU sets the interrupt mask bit and will not acknowledge the maskable request. During the last cycle, the CPU fetches vectors depicted in Table 1 and transfers their contents to the program counter and branches to the service routine.

The CPU uses the external interrupt pins,  $\overline{IRQ_1}$  and  $\overline{IRQ_2}$ , also as port pins  $P_{50}$  and  $P_{51}$ , so it provides an enable bit to Bit 0 and 1 of the RAM port 5 control register at \$0014. Refer to "RAM/PORT 5 CONTROL REGISTER" for the details.

When one of the internal interrupts, ICI, OCI, TOI, CMI or SIO is generated, the CPU produces internal interrupt signal (IRQ<sub>3</sub>). IRQ<sub>3</sub> functions just the same as  $\overline{IRQ_1}$  or  $\overline{IRQ_2}$  except for its vector address. Fig. 13 shows the block diagram of the interrupt circuit.

Table 1 Interrupt Vector Memory Map

| 0        | Ve   | ctor   | Interrupt                         |

|----------|------|--------|-----------------------------------|

| Priority | MSB  | LSB    | interrupt                         |

| Highest  | FFFE | FFFF   | RES                               |

| <b>†</b> | FFEE | FFEF   | TRAP                              |

| ]        | FFFC | FFFD   | NMI                               |

|          | FFFA | • FFFB | SWI (Software Interrupt)          |

|          | FFF8 | FFF9   | IRQ <sub>1</sub>                  |

|          | FFF6 | FFF7   | ICI (Timer 1 Input Capture)       |

|          | FFF4 | FFF5   | OCI (Timer 1 Output Compare 1, 2) |

|          | FFF2 | FFF3   | TOI (Timer 1 Overflow)            |

|          | FFEC | FFED   | CMI (Timer 2 Counter Match)       |

|          | FFEA | FFEB   | ÎRQ <sub>2</sub>                  |

| Lowest   | FFF0 | FFF1   | SIO (RDRF+ORFE+TDRE)              |

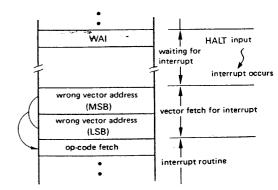

"Low" when the CPU is in the interrupt wait state after having executed the WAI, the CPU makes BA "High" and releases the buses. And when the  $\overline{HALT}$  becomes "High", the CPU returns to the interrupt wait state.

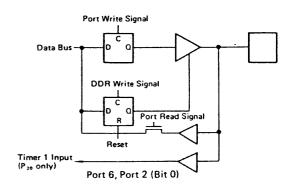

#### PORT

The HD6303X provides three I/O ports. Table 2 gives the address of ports and the data direction register and Fig. 14 the block diagrams of each port.

Table 2 Port and Data Direction Register Address

| Port   | Port Address | Data Direction Register |

|--------|--------------|-------------------------|

| Port 2 | \$0003       | \$0001                  |

| Port 5 | \$0015       | <del>-</del>            |

| Port 6 | \$0017       | \$0016                  |

#### Port 2

An 8-bit input/output port. The data direction register (DDR) of port 2 controls the I/O state. It provides two bits;

Port Write Signal

Port Output Enable

Data Bus

Timer, SCI

Output Enable

Tri-state

Timer 1, 2, SCI Input

Port 2

Port 5

Port Read Signal

Port Read Signal

bit 0 decides the I/O direction of  $P_{20}$  and bit 1 the I/O direction of  $P_{21}$  to  $P_{27}$  ("0" for input, "1" for output).

Port 2 is also used as an I/O pin for the timers and the SCI. When used as an I/O pin for the timers and the SCI, port 2 except  $P_{20}$  automatically becomes an input or an output depending on their functions regardless of the data direction register's value.

Port 2 Data Direction Register

A reset clears the DDR of port 2 and configures port 2 as an input port. This port can drive one TTL and 30pF capacitance. In addition, it can produce 1mA current when  $V_{out} = 1.5V$  to drive directly the base of Darlington transistors.

Figure 14 Port Block Diagram

Control

### • Port 5

Data Bus

An 8-bit port for input only. The lower four bits are also usable as input pins for interrupt, MR and  $\overline{HALT}$ .

### • Port 6

An 8-bit I/O port. This port provides an 8-bit DDR corresponding to each bit and can specify input or output by the bit ("0" for input, "1" for output). This port can drive one TTL load and 30pF capacitance. A reset clears the DDR of port 6. In addition, it can produce 1mA current when  $V_{out} = 1.5V$  to drive directly the base of Darlington transistors.

### BUS

### D₀~D₁

These pins are data bus and can drive one TTL load and 90pF capacitance respectively.

### • A<sub>0</sub>~A<sub>1</sub>

These pins are address bus and can drive one TTL load and 90pF capacitance respectively.

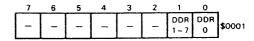

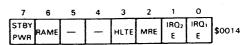

### ■ RAM/PORT 5 CONTROL REGISTER

The control register located at \$0014 controls on-chip RAM and port 5.

### **RAM/Port 5 Control Register**

### Bit 0, Bit 1 IRQ1, IRQ2 Enable Bit (IRQ1E, IRQ2E)

When using P<sub>50</sub> and P<sub>51</sub> as interrupt pins, write "1" in these bits. When "0", the CPU doesn't accept an external interrupt or a sleep cancellation by the external interrupt. These bits become "0" during reset.

### Bit 2 Memory Ready Enable Bit (MRE)

When using  $P_{52}$  as an input for Memory Ready signal, write "1" in this bit. When "0", the memory ready function is pro-

Table 3 Internal Register

| Address | Registers                          | R/W*** | Initialize at RESET |

|---------|------------------------------------|--------|---------------------|

| 17      | Port 6                             | R/W    | Undefined           |

| 18*     | -                                  |        | -                   |

| 19      | Output Compare Register 2 ("High") | R/W    | \$FF                |

| 1A      | Output Compare Register 2 ("Low")  | R/W    | \$FF                |

| 1B      | Timer Control/Status Register 3    | R/W    | \$20                |

| 1C      | Time Constant Register             | W      | \$FF                |

| 1D      | Timer 2 Up Counter                 | R/W    | \$00                |

| 1E      | -                                  | _      |                     |

| 1F**    | Test Register                      | _      |                     |

External Address.

<sup>\*\*\*</sup> R : Read Only Register

W : Write Only Register

R/W: Read/Write Register

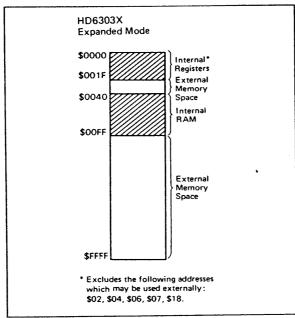

Figure 16 HD6303X Memory Map

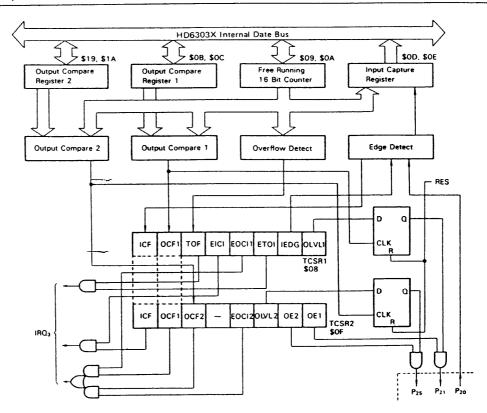

### TIMER 1

The HD6303X provides a 16-bit programmable timer which can simultaneously measure an input waveform and generate two independent output waveforms. The pulse widths of both input/output waveforms vary from microseconds to seconds.

Timer 1 is configurated as follows (refer to Fig. 18).

- · Control/Status Register 1 (8 bit)

- · Control/Status Register 2 (7 bit)

- Free Running Counter (16 bit)

- · Output Compare Register 1 (16 bit)

- · Output Compare Register 2 (16 bit)

- · Input Capture Register (16 bit)

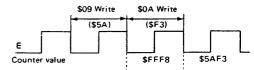

## • Free-Running Counter (FRC) (\$0009 : 000A)

The key timer element is a 16-bit free-running counter driven

and incremented by system clock. The counter value is readable by software without affecting the counter. The counter is cleared by reset.

When writing to the upper byte (\$09), the CPU writes the preset value (\$FFF8) into the counter (address \$09, \$0A) regardless of the write data value. But when writing to the lower byte (\$0A) after the upper byte writing, the CPU writes not only the lower byte data into lower 8 bit, but also the upper byte data into higher 8 bit of the FRC.

The counter will be as follows when the CPU writes to it by double store instructions (STD, STX etc.).

In the case of the CPU write (\$5AF3) to the FRC Figure 17 Counter Write Timing

## Output Compare Register (OCR)

(\$000B, \$000C; OCR1) (\$0019, \$001A; OCR2)

The output compare register is a 16-bit read/write register which can control an output waveform. The data of OCR is always compared with the FRC.

When the data matches, output compare flag (OCF) in the timer control/status register (TCSR) is set. If an output enable bit (OE) in the TCSR2 is "1", an output level bit (OLVL) in the TCSR will be output to bit 1 (Tout 1) and bit 5 (Tout 2) of port 2. To control the output level again by the next compare, the value of OCR and OLVL should be changed. The OCR is set to \$FFFF at reset. The compare function is inhibited for a cycle just after a write to the OCR or to the upper byte of the FRC. This is to begin the comparison after setting the 16-bit value valid in the register and to inhibit the compare function at this cycle, because the CPU writes the upper byte to the FRC, and at the next cycle the counter is set to \$FFF8.

\* For data write to the FRC or the OCR, 2-byte transfer instruction (such as STX etc.) should be used.

## Input Capture Register (ICR) (\$000D : 000E)

The input capture register is a 16-bit read only register which stores the FRC's value when external input signal transition

<sup>\*\*</sup> Test Register. Do not access to this register.

Figure 18 Timer 1 Block Diagram

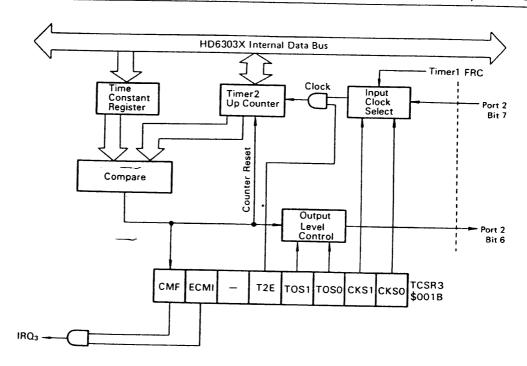

### ■ TIMER 2

In addition to the timer 1, the HD6303X provides an 8-bit reloadable timer, which is capable of counting the external event. This timer 2 contains a timer output, so the MPU can generate three independent waveforms (refer to Fig. 19).

The timer 2 is configured as follows:

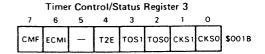

Control/Status Register 3 (7 bit)

8-bit Up Counter

Time Constant Register (8 bit)

### • Timer 2 Up Counter (T2CNT) (\$001D)

This is an 8-bit up counter which operates with the clock decided by CKS0 and CKS1 of the TCSR3. The CPU can read the value of the counter without affecting the counter. In addition, any value can be written to the counter by software even during counting.

The counter is cleared when a match occurs between the counter and the TCONR or during reset.

If a write operation is made by software to the counter at the cycle of counter clear, it does not reset the counter but put the write data to the counter.

### Time Constant Register (TCONR) (\$001C)

The time constant register is an 8-bit write only register. It is always compared with the counter.

When a match has occurred, counter match flag (CMF) of the timer control status register 3 (TCSR3) is set and the value selected by TOSO and TOSI of the TCSR3 will appear at port 2, bit 6. When CMF is set, the counter will be cleared simultaneously and then start counting from \$00. This enables regular interrupts and waveform outputs without any software support. The TCONR is set to "\$FF" during reset.

## • Timer Control/Status Register 3 (TCSR3) (\$001B)

The timer control/status register 3 is a 7-bit register. All bits are readable and 6 bits except for CMF can be written.

The followings are each pin descriptions.

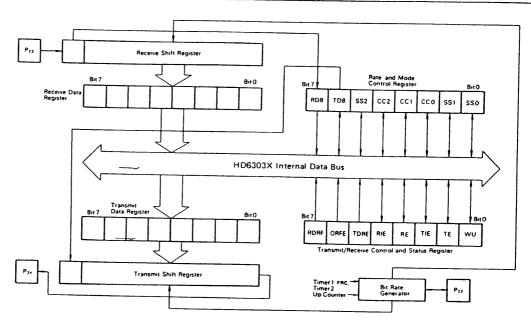

### ■ SERIAL COMMUNICATION INTERFACE (SCI)

The HD6303X SCI contains two operation modes; one is an asynchronous mode by the NRZ format and the other is a clocked synchronous mode which transfers data synchronizing with the serial clock.

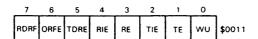

The SCI consists of the following registers as shown in Fig. 20 Block Diagram:

- · Control/Status Register (TRCSR)

- Rate/Mode Control Register (RMCR)

- Receive Data Register (RDR)

- Receive Data Shift Register (RDSR)

- · Transmit Data Register (TDR)

- · Transmit Data Shift Register (TDSR)

The serial I/O hardware requires an initialization by software for operation. The procedure is usually as follows:

- Write a desirable operation mode into each corresponding control bit of the RMCR.

- Write a desirable operation mode into each corresponding control bit of the TRCSR.

When using bit 3 and 4 of port 2 for serial I/O only, there is no problem even if TE and RE bit are set. But when setting the baud rate and operation mode, TE and RE should be "0". When clearing TE and RE bit and setting them again, more than 1 bit cycle of the current baud rate is necessary. If set in less than 1 bit cycle, there may be a case that the internal transmit/receive initialization fails.

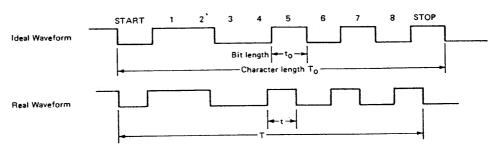

### Asynchronous Mode

An asynchronous mode contains the following two data formats:

1 Start Bit + 8 Bit Data + 1 Stop Bit

1 Start Bit + 9 Bit Data + 1 Stop Bit

In addition, if the 9th bit is set to "1" when making 9 bit data format, the format of

1 Start bit + 8 Bit Data + 2 Stop Bit is also transferred.

Data transmission is enabled by setting TE bit of the TRCSR, then port 2, bit 4 will become a serial output independently of the corresponding DDR.

For data transmit, both the RMCR and TRCSR should be set under the desirable operating conditions. When TE bit is set during this process, 10 bit preamble will be sent in 8-bit data format and 11 bit in 9-bit data format. When the preamble is produced, the internal synchronization will become stable and the transmitter is ready to act.

The conditions at this stage are as follows.

If the TDR is empty (TDRE=1), consecutive 1's are produced to indicate the idle state. 2) If the TDR contains data (TDRE=0), data is sent to the transmit data shift register and data transmit starts.

During data transmit, a start bit of "0" is transmitted first. Then 8-bit or 9-bit data (starts from bit 0) and a stop bit "1" are transmitted.

When the TDR is "empty", hardware sets TDRE flag bit. If the CPU doesn't respond to the flag in proper timing (the TDRE is in set condition till the next normal data transfer starts from the transmit data register to the transmit sift register), "1" is transferred instead of the start bit "0" and continues to be transferred till data is provided to the data register. While the TDRE is "1", "0" is not transferred.

Data receive is possible by setting RE bit. This makes port 2, bit 3 be a serial input. The operation mode of data receive is decided by the contents of the TRCSR and RMCR. The first "0" (space) synchronizes the receive bit flow. Each bit of the following data will be strobed in the middle. If a stop bit is not "1", a framing error assumed and ORFE is set.

When a framing error occurs, receive data is transferred to the receive data register and the CPU can read error-generating data. This makes it possible to detect a line break.

If the stop bit is "1", data is transferred to the receive data register and an interrupt flag RDRF is set. If RDRF is still set when receiving the stop bit of the next data, ORFE is set to indicate overrun generation.

When the CPU read the receive data register as a response to RDRF flag or ORFE flag after having read TRCS, RDRF or ORFE is cleared.

(Note) Clock Source in Asynchronous Mode

If CC1: CC0 = 10, the internal bit rate clock is provided at  $P_{22}$  regardless of the values for TE or RE. Maximum clock rate is  $E\div 16$ .

If both CC1 and CC0 are set, an external TTL compatible clock must be connected to  $P_{22}$  at sixteen times (16×) the desired bit rate, but not greater than E.

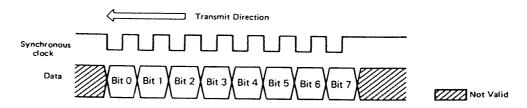

### Clocked Synchronous Mode

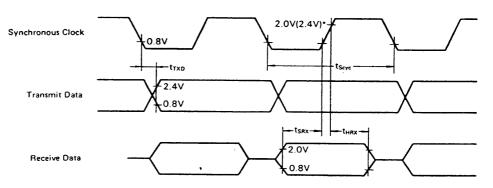

In the clocked synchronous mode, data transmit is synchronized with the clock pulse. The HD6303X SCI provides functionally independent transmitter and receiver which makes full duplex operation possible in the asynchronous mode. But in the clocked synchronous mode an SCI clock I/O pin is only  $P_{22}$ , so the simultaneous receive and transmit operation is not available. In this mode, TE and RE should not be in set condition ("1") simultaneously. Fig. 21 gives a synchronous clock and a data format in the clocked synchronous mode.

Transmit/Receive Control Status Register

### Bit 0 WU Wake-up

In a typical multi-processor configuration, the software protocol provides the destination address at the first byte of the message. In order to make uninterested MPU ignore the remaining message, a wake-up function is available. By this, uninterested MPU can inhibit all further receive processing till the next message starts.

Then wake-up function is triggered by consecutive 1's with 1 frame length (10 bits for 8-bit data, 11 for 9-bit). The software protocol should provide the idle time between messages.

By setting this bit, the MPU stops data receive till the next message. The receive of consecutive "1" with one frame length wakes up and clears this bit and then the MPU restarts receive operation. However, the RE flag should be already set before setting this bit. In the clocked synchronous mode WU is not available, so this bit should not be set.

### Bit 1 TE Transmit Enable

When this bit is set, transmit data will appear at port 2, bit 4 after one frame preamble in asynchronous mode, while in clocked synchronous mode it appears immediately. This is executed regardless of the value of the corresponding DDR. When TE is cleared, the serial I/O doesn't affect port 2, bit 4.

### Bit 2 TIE Transmit Interrupt Enable

When this bit is set, an internal interrupt (IRQ3) is enabled when TDRE (bit 5) is set. When cleared, the interrupt is inhibited.

### Bit 3 RE Receive Enable

When set, a signal is input to the receiver from port 2, bit 3 regardless of the value of the DDR. When RE is cleared, the serial I/O doesn't affect port 2, bit 3.

### Bit 4 RIE Receive Interrupt Enable

When this bit is set, an internal interrupt, IRQ3 is enabled when RDRF (bit 7) or ORFE (bit 6) is set. When cleared, the interrupt is inhibited.

### Bit 5 TDRE Transmit Data Register Empty

TDRE is set when the TDR is transferred to the transmit data shift register in the asynchronous mode, while in clocked synchronous mode when the TDSR is "empty". This bit is reset by reading the TRCSR and writing new transmit data to the transmit data register. TDRE is set to "1" during reset.

(Note) TDRE should be cleared in the transmittable state after the TE set.

## the TE set. Bit 6 ORFE Overrun Framing Error

ORFE is set by hardware when an overrun or a framing error is generated (during data receive only). An overrun error occurs when new receive data is ready to

be transferred to the RDR during RDRF still being set. A framing error occurs when a stop bit is "0". But in clocked synchronous mode, this bit is not affected. This bit is cleared when reading the TRCSR, then the RDR, or during reset.

### Bit 7 RDRF Receive Data Register Full

RDRF is set by hardware when the RDSR is transferred to the RDR. Cleared when reading the TRCSR, then the RDR, or during reset.

(Note) When a few bits are set between bit 5 to bit 7 in the TRCSR, a read of the TRCSR is sufficient for clearing those bits. It is not necessary to read the TRCSR everytime to clear each bit.

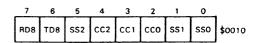

## Transmit Rate/Mode Control Register (RMCR)

The RMCR controls the following serial I/O:

- · Baud Rate

- · Data Format

- · Clock Source

- · Port 2, Bit 2 Function

In addition, if 9-bit data format is set in the asynchronous mode, the 9th bit is put in this register. All bits are readable and writable except bit 7 (read only). This register is set to \$00 during reset.

### Transfer Rate/Mode Control Register

| Bit 0 | SS0]       |              |

|-------|------------|--------------|

| Bit 1 | SS1<br>SS2 | Speed Select |

| Bit 5 | SS2        |              |

These bits control the baud rate used for the SCI. Table 6 lists the available baud rates. The timer 1 FRC (SS2=0) and the timer 2 up counter (SS2=1) provide the internal clock to the SCI. When selecting the timer 2 as a baud rate source, it functions as a baud rate generator. The timer 2 generates the baud rate listed in Table 7 depending on the value of the TCONR.

(Note) When operating the SCI with internal clock, do not perform write operation to the timer/counter which is the clock source of the SCI.

| Bit 2<br>Bit 3<br>Bit 4 | CC0 CC1 CC2 | Clock Control/Format Select |

|-------------------------|-------------|-----------------------------|

| Bit 4                   | CC2         |                             |

These bits control the data format and the clock source (refer to Table 8).

\* CC0, CC1 and CC2 are cleared during reset and the MPU goes to the clocked synchronous mode of the external clock operation. Then the MPU sets port 2, bit 2 into the clock input state. When using port 2, bit 2 as an output port, the DDR of port 2 should be set to "1" and CC1 and CC0 to "0" and "1" respectively.

Table 8 SCI Format and Clock Source Control

| CC2 | CC1 | CC0 | Format     | Mode                | Clock Source | Port 2, Bit 2 | Port 2, Bit 3                       | Port 2, Bit 4  |

|-----|-----|-----|------------|---------------------|--------------|---------------|-------------------------------------|----------------|

| 0   | 0   | 0   | 8-bit data | Clocked Synchronous | External     | Input         | )                                   |                |

| 0   | 0   | 1   | 8-bit data | Asynchronous        | Internal     | Not Used**    |                                     | DE 1 1 1 1/4/1 |

| 0   | 1   | 0   | 8-bit data | Asynchronous        | Internal     | Output*       | When the TRCSR bit 3 is used as a s | •              |

| 0   | 1   | 1   | 8-bit data | Asynchronous        | External     | Input         | Dit 3 is used as a s                | eriai input.   |

| 1   | 0   | 0   | 8-bit data | Clocked Synchronous | Internal     | Output        |                                     |                |

| 1   | 0   | 1   | 9-bit data | Asynchronous        | Internal     | Not Used**    |                                     |                |

| 1   | 1   | 0   | 9-bit data | Asynchronous        | Internal     | Output*       | When the TRCSR                      | •              |

| 1   | 1   | 1   | 9-bit data | Asynchronous        | External     | Input         | Dit 4 is used as a s                | eriai output.  |

<sup>\*</sup> Clock output regardless of the TRCSR, bit RE and TE.

Caution for clock-synchronous serial communication interface

When transmitting through clock-synchronous serial communication interface, TE bit should not be cleared with TDRE of TRCSR (\$11) is "0".

The TDRE set and clear conditions of SCI are shown as follows.

|      | Set condition                                                                                                                                    | Clear condition                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| TDRE | <ol> <li>TDR → transmit shift register (asynchronous)</li> <li>Transmit shift register is empty. (clock-synchronous)</li> <li>RES = 0</li> </ol> | When writing to TDR after TRSCR read, with TDRE = 1, TDRE is cleared. |

If transmit data is written to TDR, and then TE bit is cleared with TDRE = 0 to stop transmitting, TDRE remains "0".

In this case, even if TE bit is set and transmit data is written again, the TDR data is not transmitted.

Please note that TE bit must be cleared after the last data has been transmitted.

(This caution is not applied to asynchronous serial communication interface.)

### Bit 6 TD8 Transmit Data Bit 8

When selecting 9-bit data format in the asynchronous mode, this bit is transmitted as the 9th data. In transmitting 9-bit data, write the 9th data into this bit then write data to the receive data register.

### Bit 7 RD8 Receive Data Bit 8

When selecting 9-bit data format in the asynchronous mode, this bit stores the 9th bit data. In receiving 9-bit data, read this bit then the receive data register.

### ■ TIMER, SCI STATUS FLAG

Table 9 shows the set and reset conditions of each status flag in the timer 1, timer 2 and SCI.

As for Timer 1 and Timer 2 status flag, if the set and reset condition occur simultaneously, the set condition is prior to the reset condition. But in case of SCI control status flag, the reset condition has priority. Especially as for OCF1 and OCF2 of Timer 1, the set signal is generated periodically whenever FRC matches OCR after the set, and which can cause the unclear of the flag. To clear surely, the method is necessary to avoid the occurence of the set signal between TCSR Read and OCR write. For example, match the OCR value to FRC first, and next read TCSR, and then write OCR at once.

<sup>\*\*</sup> Not used for the SCI.

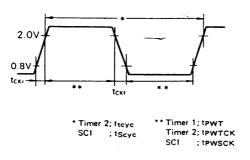

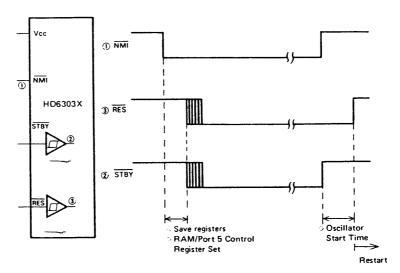

Figure 22 Standby Mode Timing

### TRAP FUNCTION

The CPU generates an interrupt with the highest priority (TRAP) when fetching an undefined instruction or an instruction from non-memory space. The TRAP prevents the systemburst caused by noise or a program error.

### Op Code Error

When fetching an undefined op code, the CPU saves CPU registers as well as a normal interrupt and branches to the TRAP (SFFEE, SFFEF). This has the priority next to reset.

Address Error When an instruction fetch is made from internal register (\$0000~\$001F), the MPU generates an interrupt as well as an op code error. But on the system with no memory in its external memory area, this function is not applicable if an instruction fetch is made from the external non-memory area.

This function is available only for an instruction fetch and is not applicable to the access of normal data read/write.

(Note) The TRAP interrupt provides a retry function differently from other interrupts. This is a program flow return to the address where the TRAP occurs when a sequence returns to a main routine from the TRAP interrupt routine by RTI. The retry can prevent the system burst caused by noise etc.

However, if another TRAP occurs, the program repeats the TRAP interrupt forever, so the consideration is necessary in programming.

### ■ INSTRUCTION SET

The HD6303X provides object code upward compatible with the HD6801 to utilize all instruction set of the HMCS6800. It also reduces the execution times of key instructions for throughput improvement.

Bit manipulation instruction, change instruction of the index register and accumulator and sleep instruction are also added.

The followings are explained here.

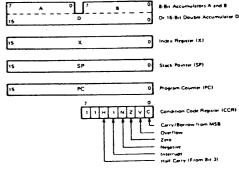

- CPU Programming Model (refer to Fig. 23)

- Addressing Mode

- Accumulator and Memory Manipulation Instruction (refer to Table 10)

- New Instruction

- Index Register and Stack Manipulation Instruction (refer to Table 11)

- Jump and Branch Instruction (refer to Table 12)

- Condition Code Register Manipulation (refer to Table 13)

- Op Code Map (refer to Table 14)

### Programming Model

Fig. 23 depicts the HD6303X programming model. The double accumulator D consists of accumulator A and B, so when using the accumulator D, the contents of A and B are destroyed.

Figure 23 CPU Programming Model

### CPU Addressing Mode

The HD6303X provides 7 addressing modes. The addressing mode is decided by an instruction type and code. Table 10 through 14 show addressing modes of each instruction with the execution times counted by the machine cycle.

When the clock frequency is 4 MHz, the machine cycle time

Table 10 Accumulator, Memory Manipulation Instructions

|                            |          |                |          |          |              |              | Ada      | Iressi   | ng l     | Mod            | es                                               |          |          |           |              |               |                                                       | Condition Code<br>Register |   |    |    |   |    |  |  |

|----------------------------|----------|----------------|----------|----------|--------------|--------------|----------|----------|----------|----------------|--------------------------------------------------|----------|----------|-----------|--------------|---------------|-------------------------------------------------------|----------------------------|---|----|----|---|----|--|--|

| Operations                 | Mnemonic | IMI            | ME       | 5        | DIF          | REC          | Т        | IN       | DE:      | ×              | EXT                                              | EN       | O        | IMF       | LIE          | D             | Boolean/<br>Arithmetic Operation                      | 5                          | 4 | 3  | 2  | 1 | o  |  |  |

|                            |          | ОР             | ~        | #        | OP           | ~            | #        | OP       | ~        | #              | OP                                               | ~        | #        | ОP        | ~            | #             | Antimetic Operation                                   | н                          | 1 | N  | z  | v | С  |  |  |

| Add                        | ADDA     | 88             | 2        | 2        | 98           | 3            | 2        | A8       | 4        | 2              | 88                                               | 4        | 3        |           |              |               | A + M→ A                                              | 1                          | • | ı  | 1  | 1 | 1  |  |  |

|                            | ADDB     | СВ             | 2        | 2        | DB           | 3            | 2        | E8       | 4        | 2              | FB                                               | 4        | 3        |           |              |               | B + M → 8                                             | t                          | • | 1  | 1  | 1 | 1  |  |  |

| Add Double                 | ADDD     | СЗ             | 3        | 3        | D3           | 4            | 2        | E3       | 5        | 2              | F3                                               | 5        | 3        |           |              |               | A:B+M:M+1-A:B                                         | •                          | • | 1  | 1  | ī | 1  |  |  |

| Add Accumulators           | ABA      | T              | _        |          |              |              |          |          |          |                |                                                  |          |          | 18        | 1            | 1             | $A + B \rightarrow A$                                 | 1                          | • | 1  | ı  | 1 | 1  |  |  |

| Add With Carry             | ADCA     | 89             | 2        | 2        | 99           | 3            | 2        | Α9       | 4        | 2              | В9                                               | 4        | 3        |           |              |               | A + M + C → A                                         | 1                          | • | :  | 1  | 1 | :  |  |  |

|                            | ADCB     | C9             | 2        | 2        | D9           | 3            | 2        | E9       | 4        | 2              | F9                                               | 4        | 3        |           |              |               | B + M + C → B                                         | 1                          | • | t  | 1  | : | 1  |  |  |

| AND                        | ANDA     | 84             | 2        | 2        | 94           | 3            | 2        | A4       | 4        | 2              | B4                                               | 4        | 3        |           |              |               | A·M → A                                               | •                          | • | 1  | :  | Я | •  |  |  |

| i                          | ANDB     | C4             | 2        | 2        | 04           | 3            | 2        | E4       | 4        | 2              | F4                                               | 4        | 3        |           |              |               | B·M → B                                               | •                          | • | 1  | 1  | R | •  |  |  |

| Bit Test                   | BITA     | 85             | 2        | 2        | 95           | 3            | 2        | A5       | 4        | 2              | 85                                               | 4        | 3        |           | <b>—</b>     |               | A-M                                                   | •                          | • | ī  | :  | R | •  |  |  |

|                            | BITB     | C5             | 2        | 2        | D5           | 3            | 2        | €5       | 4        | 2              | F 5                                              | 4        | 3        | <b></b> - |              | $\vdash$      | в-м                                                   | •                          | • | 1  | 1  | R | ١. |  |  |

| Clear                      | CLR      | +==            | Ť        | -        |              |              | 1        | 6F       | 5        | 2              | 7F                                               | 5        | 3        |           | <del> </del> | -             | 00 → M                                                | •                          | • | R  | s  | R | F  |  |  |

| <del>-</del>               | CLRA     | +              | -        | -        |              |              | $t^-$    | -        | -        |                | $\vdash$                                         | <u> </u> | $\vdash$ | 4F        | 1            | 1             | 00 A                                                  |                            |   | R  | s  | R | F  |  |  |

|                            | CLAB     | ⇟              |          | $\vdash$ | <del> </del> | $\vdash$     | 1        |          | Η-       | <u> </u>       | <del>                                     </del> | 1        | $\vdash$ | 5F        | 1            | 1             | 00 - B                                                | •                          | • | R  | s  | R | F  |  |  |

| Compare                    | CMPA     | 81             | 2        | 2        | 91           | 3            | 2        | AI       | 4        | 2              | B1                                               | 4        | 3        | -         | H            | H             | A - M                                                 | •                          |   | 1  | 1  | 1 | 1  |  |  |

| Compare                    | СМРВ     | C1             | 2        | 2        | 01           | 3            | 2        | E1       | 4        | 2              | FI                                               | 4        | 3        |           | -            | ┝             | B - M                                                 | •                          | • | 1  | 1  | 1 | 1  |  |  |

| Compare<br>Accumulators    | CBA      | -              | Ė        | -        | -            | j            | Ė        | -        | Ť        | Ė              |                                                  | Ė        | ٦        | 11        | 1            | ,             | A - B                                                 | •                          | • | 1  | :  | : | 1: |  |  |

| Complement, 1's            | сом      | <del> </del> - | +-       | 1        | ├            | <del> </del> | ÷        | 63       | 6        | 2              | 73                                               | 6        | 3        | -         | ┝            | -             | M → M                                                 |                            |   | 1  | 1  | R | s  |  |  |

| Complement, 13             | COMA     | +              | ╁        | ╁        | ├            | $\vdash$     | ├        | 03       | ۴        | 1-             | /3                                               | ۳        | ٦        | 43        | 1            | 1             | Ā → A                                                 | -                          | - | :  | 1  | A | 5  |  |  |

|                            | COMB     | <del> </del>   | ╁        | 1        | <del> </del> | ├-           | ⊢        | -        | ╁╌       | 1              | -                                                | -        | $\vdash$ | 53        | 1            | 1             | 8 →8                                                  |                            |   | :  | 1  | R | 5  |  |  |

| Complement, 2's            | NEG      | -              | ╁        | ╁        | <del> </del> | ┝            | ╁╴       | 60       | 6        | 2              | 70                                               | 6        | 2        | 133       | ŀ            | ŀ             | 00 - M → M                                            | •                          | • | :  | 1  | 0 | _  |  |  |

| (Negate)                   | NEGA     | +              | $\vdash$ | 1        | +            | ┢            | ╁        | -        | ۲        | -              | 10                                               | ۲        | ۲        | 40        | 1            | 1             | 00 - A → A                                            | •                          |   | i  | ÷  | o | C  |  |  |

| (Negate)                   | NEGB     | -              | ╁        | -        |              | ⊢            | ╁        | -        | ┢        | <del>  -</del> | ├─                                               | +-       | ┝        | 50        | 1            | i,            | 00 - B → B                                            |                            | • | i  | ÷  | 6 | +  |  |  |

| Decimal Adjust, A          | DAA      |                | T        | $\vdash$ |              |              | T        | -        | $\vdash$ | $\vdash$       | $I^-$                                            |          |          | 19        | 2            | ,             | Converts binary add of BCD characters into BCD format | •                          | • | ;  | :  | 1 | a  |  |  |

| Decrement                  | DEC      | +              | +        | $\vdash$ | +-           | -            | +        | 6A       | 6        | 2              | 7A                                               | 6        | 3        | ├         | H            | -             | M - 1 → M                                             | •                          |   | 1  | 1  | 0 | ١, |  |  |

| Decrement                  | DECA     | +-             | ╁        | ╁        | $\vdash$     | ⊢            | +-       | -        | +        | ⊢              |                                                  | F        | F        | 4A        | 1            | 1             | A - 1 → A                                             | -                          |   | 1  | 1  | 0 | ١, |  |  |

|                            | DECB     | ╁─╌            | ╁╴       | ╁        | ┼─           | ╁            | +        | -        | +-       | ┢              | -                                                | ┼-       | ⊢        | 5A        | 1            | 1             | 8 - 1 → 8                                             |                            | - | 1  | 1  | 0 | ╄  |  |  |

| Exclusive OR               | EORA     | 88             | 2        | 2        | 98           | 3            | 2        | A8       | 4        | 2              | В8                                               | 4        | 3        | 37        | <u>ا</u>     | ١÷            | A ⊕ M → A                                             | •                          |   | 1  | 1  | R | ١. |  |  |

| EXCIDSIVE OF               | EORB     | C8             | 2        | 2        | D8           | 3            | 2        | E8       | 4        | 2              | F8                                               | 4        | 3        | ├         | ╁            | -             | 8 ⊕ M→ 8                                              | •                          | • | 1  | i  | B | +  |  |  |

| Increment                  | INC      | 100            | +-       | 12       | 100          | 13           | 1        | 6C       | 6        | -              | 7C                                               | 6        | 3        | ├         | -            | ⊢             | M + 1 → M                                             | •                          | • | :  | 1  | 6 | ١. |  |  |

| increment                  |          | +              | ╁        | ╁        | 1            | ╁            | +;       | 100      | 10       | -              | 1.0                                              | 10       | ۲        | 4C        | +            | 1             | A + 1 - A                                             |                            | - | 1  | 1  | 3 | -  |  |  |

|                            | INCA     | ╁              | +-       | ╁        | ┼            | ⊢            | ╀        | $\vdash$ | ⊢        | ╁              | -                                                | ┢        | -        | 5C        | 1            | 1             | 8+1-8                                                 |                            | - | :  | 1: | 0 | L  |  |  |

|                            | INCB     | 100            | +        | -        | -            | +-           | -        | 1        | +        | -              | 100                                              | 4        | -        | 50        | 1            | 1 3           | <del>                                     </del>      | :                          | - | ;  | 1: | R |    |  |  |

| Load<br>Accumulator        | LDAA     | 86             | 2        | 2        | 96           | 3            | 2        | A6       | 4        | 2              | B6                                               | +-       | 3        | ├         | ┝            | ⊢             | M - A                                                 | ŀ                          |   | ;  | 1: | R | +  |  |  |

| Load Double<br>Accumulator | LDAB     | C6<br>CC       | 3        | +        | D6<br>DC     | 4            | 2        | E6       | 5        | 2              | FC                                               | 5        | 3        | <u> </u>  | ╁            | ┢             | M → B<br>M + 1 → B, M → A                             | •                          | • | ;  | ;  | R |    |  |  |

| Multiply Unsigned          | MUL      | +              | +        | +        | +-           | ╁            | ╁        |          | +        | +-             | $\vdash$                                         | +        | +        | 3D        | 7            | 1             | A x B → A : B                                         | •                          | • |    | -  | • | 6  |  |  |

| OR, Inclusive              | ORAA     | 8.8            | 2        | 2        | 9A           | 3            | 2        | AA       | 4        | 2              | ВА                                               | 4        | 3        | 133       | <del> </del> | <del>ļ'</del> | A+M-A                                                 |                            | • | 1  | 1  | R | f. |  |  |

| On, meiusive               | ORAB     | CA             | -        | _        | DA           | -            | 2        | EA       | 4        | 2              | FA                                               | 4        | 3        | -         | +-           | -             | B+M- B                                                | •                          | • | :  | ÷  | A | +  |  |  |

| Push Data                  | PSHA     | +-             | 1        | +-       | 104          | -            | 1        | 157      | +        | Ļ              | · ^                                              | ╀        | ۲        | 36        | 4            | 1             | A → Msp, SP – 1 → SP                                  | •                          | - | ÷  | ŀ  |   | Ŧ, |  |  |

| rusn Data                  |          | +              | +-       | +-       | +-           | ⊢            | +        | -        | ├-       | ├              | ├                                                | $\vdash$ | Ͱ        | 37        | 4            | 1             | B → Msp, SP - 1 → SP                                  | -                          | • |    |    |   | +  |  |  |

| Bull Cons                  | PSHB     | +-             | ╁        | +        | ╁            | ╁            | ╁        | -        | +-       | +-             | <del> </del> -                                   | ╁        | ╁        |           | 3            | +-            | $SP + 1 \rightarrow SP, Msp \rightarrow A$            |                            |   |    | -  | - | +  |  |  |

| Pull Data                  | PULA     | +              | ╁        | +        | $\vdash$     | +-           | +        | ├-       | +        | ╁              | $\vdash$                                         | +        | -        | 32        | 3            | 1             | $SP + 1 \rightarrow SP, Msp \rightarrow B$            |                            | • | -  | •  | - | ۲, |  |  |

| O                          | PULB     | +-             | +        | +        | $\vdash$     | $\vdash$     | +        | 60       | -        | 1-             | 79                                               | -        | -        | 33        | 13           | ١,            | or + i → or, msp → d                                  | -                          |   | 1: | 1  | 0 | +  |  |  |

| Rotate Left                | ROL      | 1-             | +        | +        | $\vdash$     | +            | +        | 69       | 6        | 2              | 1,9                                              | P        | 3        | 49        | +            | ١.            | M) [                                                  | ŀ                          | • | 1; | -  | + | +  |  |  |

|                            | ROLA     | +              | ╀        | ╀        | ⊢            | $\vdash$     | $\vdash$ | -        | ╁        | Ͱ              | -                                                | $\vdash$ | ╀        |           | 1            | 1             | 1. 4. 4. 4. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.    | -                          | + | 1; | 1: | 0 | L  |  |  |

|                            | ROLB     | -              | +        | $\perp$  | ┼            | $\vdash$     | 1        | 100      | 1        | 1-             | 70                                               | 1        | 1        | 59        | 1            | Ľ             | ļ*                                                    | :                          | ŀ | 1  |    | ᆫ | L  |  |  |

| Rotate Right               | ROR      | +-             | +        | +        | +-           | +-           | +        | 66       | 10       | 1              | 76                                               | 10       | 3        | 45        | +-           | 1.            | 4 TTTTTT                                              |                            | ÷ | 1  | 1  | 6 | -  |  |  |

|                            | RORA     | _ L            | Ь.       | L        | _            | L.           | 1        | L        | L.       | L.             | L.                                               | 1        | <u>L</u> | 46        | 1            | 1             | ] ^                                                   | •                          |   | 1  | 1; | 6 | 4  |  |  |

(Note) Condition Code Register will be explained in Note of Table 13.

(continued)

### Additional Instruction

In addition to the HD6801 instruction set, the HD6303X prepares the following new instructions.

$$AIM \ldots (M) \cdot (IMM) \rightarrow (M)$$

Executes "AND" operation to immediate data and the memory contents and stores its result in the memory.

OIM ....

$$(M) + (IMM) \rightarrow (M)$$

Executes "OR" operation to immediate data and the memory contents and stores its result in the memory.

$$EIM \ldots (M) \oplus (IMM) \rightarrow (M)$$

Executes "EOR" operation to immediate data and the memory contents and stores its result in the memory.

$$TIM \dots (M) \cdot (IMM)$$

Executes "AND" operation to immediate data and changes the relative flag of the condition code register.

These area 3-byte instructions; the first byte is op code, the second immediate data and the third address modifier.

$$XGDX \dots (ACCD) \leftrightarrow (IX)$$

Exchanges the contents of accumulator and the index register.

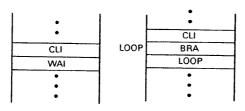

### SLP

Goes to the sleep mode. Refer to "LOW POWER DIS-SIPATION MODE" for more details of the sleep mode.

Table 11 Index Register, Stack Manipulation Instructions

|                        |          | Addressing Modes |          |    |     |     |    |    |     |   |    |     |   |     |     | Boolean/ | Condition Code<br>Register                         |   |   |   |    |   |   |

|------------------------|----------|------------------|----------|----|-----|-----|----|----|-----|---|----|-----|---|-----|-----|----------|----------------------------------------------------|---|---|---|----|---|---|

| Pointer Operations     | Mnemonic | IM               | ME       | D. | DIF | 350 | Τ: | IN | DE: | × | EX | ΓEN | D | IMP | LIE | D        | Arithmetic Operation                               | 5 | 4 | 3 | 2  | 1 | 0 |

|                        |          | OP               | -        | #  | OP  | ~   | *  | OP | ~   | # | OP | [-  | * | OP  | ~   | *        |                                                    | Ŧ | - | N | z  | > | С |

| Compare Index Reg      | CPX      | 8C               | 3        | 3  | 9C  | 4   | 2  | AC | 5   | 2 | ВС | 5   | 3 |     |     |          | X - M:M + 1                                        | • | • | : | t  | : | : |

| Decrement Index Reg    | DEX      | Τ                |          |    |     |     |    |    |     |   |    |     |   | 09  | 1   | 1        | X – 1 → X                                          | • | • | • | :  | • | • |

| Decrement Stack Potr   | DES      |                  | Γ        |    |     |     |    |    |     |   |    |     |   | 34  | 1   | 1        | SP - 1 → SP                                        | • | • | • | •  | • | • |

| Increment Index Reg    | INX      | Г                |          |    |     |     |    |    | Γ   | Г |    | П   |   | 08  | 1   | 1        | X + 1 → X                                          | • | • | • | 1  | • | • |

| Increment Stack Potr   | INS      |                  |          | Г  |     |     |    |    | Π   |   |    |     |   | 31  | 1   | 1        | SP + 1 → SP                                        | • | • | • | •  | • | • |

| Load Index Reg         | LDX      | CE               | 3        | 3  | DE  | 4   | 2  | EE | 5   | 2 | FE | 5   | 3 |     |     |          | $M \rightarrow X_H$ , $(M+1) \rightarrow X_L$      | • | • | 0 | 1  | R | • |

| Load Stack Pntr        | LDS      | 8E               | 3        | 3  | 9E  | 4   | 2  | ΑE | 5   | 2 | 88 | 5   | 3 |     |     |          | M → SPH. (M+1) → SPL                               | • |   |   | 1  | R | • |

| Store Index Reg        | STX      | T                |          | Π  | DF  | 4   | 2  | EF | 5   | 2 | FF | 5   | 3 |     |     |          | $X_H \rightarrow M, X_L \rightarrow (M+1)$         | • | • | 0 | 1: | R | • |

| Store Stack Pntr       | STS      | T                |          | Γ  | 9F  | 4   | 2  | AF | 5   | 2 | BF | 5   | 3 |     |     |          | $SP_H \rightarrow M, SP_L \rightarrow (M+1)$       | • | • | 0 | 1  | R | • |

| Index Reg → Stack Pntr | TXS      | 1                |          | T  | 1   | T   | T  |    |     |   |    |     | Π | 35  | 1   | 1        | X - 1 → SP                                         | • | • | • | •  | • | • |

| Stack Potr - Index Reg | TSX      | 1                | $\vdash$ |    | ·   | Τ   | Π  |    | T   | Г |    |     |   | 30  | 1   | 1        | SP + 1 → X                                         | • | • | • | •  | • | • |

| Add                    | ABX      | T                | Г        | Г  | T   | Г   | Γ  |    | I   |   | Π  | П   |   | 3A  | 1   | 1        | B + X → X                                          | • | • | • | •  | • | • |

| Push Data              | PSHX     |                  | 1        | Т  |     | Т   | Г  |    | Π   |   |    | Г   |   | 3C  | 5   | 1        | $X_L \rightarrow M_{sp}$ , $SP - 1 \rightarrow SP$ | • | • | • | •  | • | • |

|                        | 1        | 1                | l        | ļ  | 1   |     | -  |    |     |   |    |     |   |     |     |          | XH → MSP, SP - 1 → SP                              |   |   | L |    |   | L |

| Pull Data              | PULX     |                  | Γ        | Τ  | T   |     | T  |    | Τ   | Г |    | Г   | Γ | 38  | 4   | 1        | SP + 1 → SP, M <sub>SP</sub> → X <sub>H</sub>      | • | • | • | •  | • | • |

|                        |          |                  |          |    | l   |     | 1  |    |     |   |    | 1   |   |     |     | 1        | SP + 1 - SP, Map - XL                              | L | L | L |    |   | L |

| Exchange               | XGDX     | 1                | T        | Т  |     | T   |    |    | T   |   | Π  | Π   |   | 18  | 2   | 1        | ACCDIX                                             | • | • | • | •  | • | • |

(Note) Condition Code Register will be explained in Note of Table 13.

Table 13 Condition Code Register Manipulation Instructions

|                      |          | Addre | ssingh   | Aodes |                          | Condition Code Register |   |   |            |   |    |  |  |  |  |

|----------------------|----------|-------|----------|-------|--------------------------|-------------------------|---|---|------------|---|----|--|--|--|--|

| Operations           | Mnemonic | IM    | PLIE     | D     | <b>Boolean Operation</b> | 5                       | 4 | 3 | 2          | 1 | 0  |  |  |  |  |

|                      |          | OP    | <b>-</b> | #     |                          | н                       | 1 | N | Z          | V | C  |  |  |  |  |

| Clear Carry          | CLC      | ос    | 1        | 1     | 0 → C                    | •                       | ٠ | • | •          | • | R  |  |  |  |  |

| Clear Interrupt Mask | CLI      | 0E    | 1        | 1     | 0 → 1                    | •                       | R | • | •          | • | •  |  |  |  |  |

| Clear Overflow       | CLV      | 0A    | 1        | 1     | 0 - V                    | •                       | • | • | •          | R | •  |  |  |  |  |

| Set Carry            | SEC      | 00    | 1        | 1     | 1 → C                    | •                       | • | • | •          | • | \$ |  |  |  |  |

| Set Interrupt Mask   | SEI      | OF    | 1        | 1     | 1 1                      | •                       | s | • | •          | • | •  |  |  |  |  |

| Set Overflow         | SEV      | 08    | 1        | 1     | 1 → V                    | •                       | • | • | •          | S | •  |  |  |  |  |

| Accumulator A → CCR  | TAP      | 06    | 1        | 1     | A→ CCR                   |                         |   |   | <b>9</b> - |   | _  |  |  |  |  |

| CCR → Accumulator A  | TPA      | 07    | 1        | 1     | CCR → A                  | •                       | • |   |            | • |    |  |  |  |  |

#### LEGEND

- OP Operation Code (Hexadecimal)

- Number of MCU Cycles

- Contents of memory location pointed to by Stack Pointer Number of Program Bytes

- Arithmetic Plus

- Arithmetic Minus

- Boolean AND

- Boolean Inclusive OR

- Boolean Exclusive OR Complement of M

- Transfer into

- Bit = Zero

- 00 Byte = Zero

### CONDITION CODE SYMBOLS

- Half-carry from bit 3 to bit 4

- Interrupt mask

- Negative (sign bit)

- Zero (byte)

- Overflow, 2's complement

- Carry/Borrow from/to bit 7

- Reset Always

- Set Always

- Set if true after test or clear **‡**

- Not Affected

(Note) Condition Code Register Notes: (Bit set if test is true and cleared otherwise)

- (Bit V) Test: Result = 10000000?

- (3) (Bit C) Test: Result \ 00000000?

- (Bit C) Test: BCD Character of high-order byte greater than 10? (Not cleared if previously set)

- (Bit V) Test: Operand = 10000000 prior to execution?

- **5** (Bit V) Test: Operand = 01111111 prior to execution?

- (Bit V) Test: Set equal to NO C = 1 after the execution of instructions

- 7 (Bit N) Test: Result less than zero? (Bit 15=1)

- (All Bit) Load Condition Code Register from Stack.

- Set when interrupt occurs. If previously set, a Non-Maskable Interrupt is required to exit the wait state. (Bit 1)

- (10) (All Bit) Set according to the contents of Accumulator A.

- (Bit C) Result of Multiplication Bit 7=1? (ACCB)

Table 14 OP-Code Map

| OF   | •  |      |      |      |      | ACC  | ACC  | IND  | EXT  |      | ACCA | or SP |      | T    | ACCE | or X |      | 1        |

|------|----|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|----------|

| COL  | Œ  |      |      |      |      | Α    | В    | INU  | DIR  | IMM  | DIR  | IND   | EXT  | IMM  | DIR  | IND  | EXT  | 1        |

| 1    | 11 | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010  | 1011 | 1100 | 1101 | 1110 | 1311 | ]        |

| ro , |    | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | A     | 8    | С    | D    | E    | F    | <u>l</u> |

| 0000 | 0  |      | SBA  | BRA  | TSX  |      | NI   | EG   |      |      |      |       | SI   | UB   |      |      |      | 0        |

| 0001 | 1  | NOP  | CBA  | BRN  | INS  |      |      | А    | IM   |      |      |       | CI   | MP   |      |      |      | T        |

| 0100 | 2  |      |      | вні  | PULA |      |      | 0    | IM   |      |      |       | SI   | вс   |      |      |      | 2        |

| 0011 | 3  |      |      | BLS  | PULB |      | CC   | M    |      |      | su   | BD    |      |      | AD   | DD   |      | 3        |

| 0100 | 4  | LSRD |      | BCC  | DES  |      | L    | SR   |      |      |      |       | Al   | ND   |      |      |      | 4        |

| 0101 | 5  | ASLD |      | BCS  | TXS  |      |      | Ε    | IM   |      |      |       | В    | IT.  |      |      |      | 5        |

| 0110 | 6  | TAP  | TAB  | BNE  | PSHA |      | R    | OR   |      |      |      |       | L    | DA   |      |      |      | 6        |

| 0111 | 7  | TPA  | TBA  | BEQ  | PSH8 |      | A    | SR   |      |      |      | STA   |      |      |      | STA  |      | 7        |

| 1000 | 8  | INX  | XGDX | BVC  | PULX |      | A    | SL   |      |      |      |       | E    | OR   |      |      |      | 8        |

| 1001 | 9  | DEX  | DAA  | BVS  | RTS  |      | R    | OL   |      |      |      |       | Al   | DC.  |      |      |      | 9        |

| 1010 | A  | CLV  | SLP  | BPL  | ABX  |      | D    | EC   |      |      |      |       | O    | RA   |      |      |      | A        |

| 1011 | В  | SEV  | ABA  | ВМІ  | RTI  |      |      | 7    | IM   |      |      |       | A    | DO   |      |      |      | В        |

| 1100 | С  | CLC  |      | BGE  | PSHX |      | 11   | NC.  |      |      | C    | PX    |      |      | L    | OD   |      | С        |

| 1101 | ۵  | SEC  |      | BLT  | MUL  |      | T:   | ST   |      | 8SR  |      | JSR   |      |      |      | STD  |      | D        |

| 1110 | ε  | CLI  |      | BGT  | WAI  |      |      | JI   | МР   |      | LI   | DS    |      |      | L    | ΣX   |      | Ε        |

| 1111 | F  | SEI  |      | BLE  | SWI  |      | С    | LR   |      |      |      | STS   |      |      |      | STX  |      | F        |

|      |    | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | A     | В    | С    | D    | Ε    | F    | ] _      |

<sup>&#</sup>x27;UNDEFINED OP CODE

<sup>\*</sup> Only each instructions of AIM, OIM, EIM, TIM

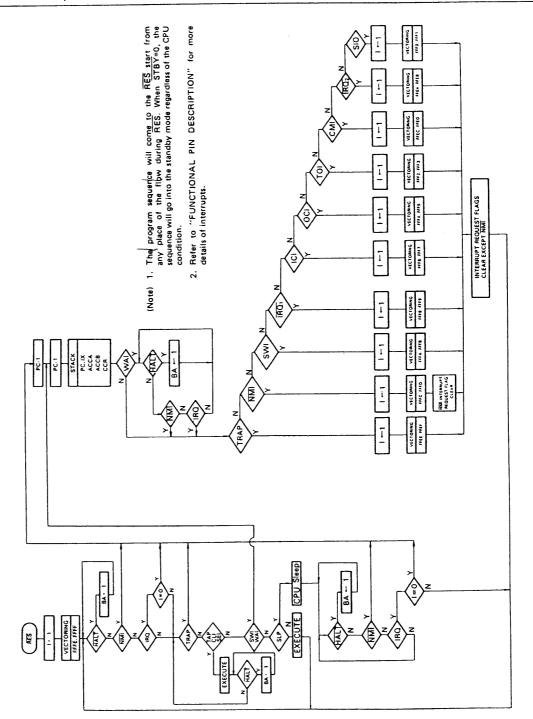

Figure 25 HD6303X System Flow Chart

|        | s Mode &<br>uctions | Cycles       | Cycle<br># | Address Bus         | R/₩                                              | RD  | WR  | LIR | Data Bus                      |

|--------|---------------------|--------------|------------|---------------------|--------------------------------------------------|-----|-----|-----|-------------------------------|

| NDEXED |                     |              |            |                     |                                                  |     |     |     |                               |

| JMP    |                     | T            | 1          | Op Code Address + 1 | 1                                                | 0   | 1   | 1   | Offset                        |

|        |                     | 3            | 2          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

|        |                     |              | 3          | Jump Address        | 1                                                | 0   | 1   | 0   | First Op Code of Jump Routine |

| ADC    | ADD                 | <del> </del> | 1          | Op Code Address + 1 | 1                                                | 0   | 1   | 1   | Offset                        |

| AND    | BIT                 |              | 2          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

| CMP    | EOR                 |              | 3          | IX + Offset         | 1                                                | 0   | 1   | 1   | Operand Data                  |

| LDA    | ORA                 | 4            | 4          | Op Code Address + 2 | 1                                                | 0   | 1   | 0   | Next Op Code                  |

| SBC    | SUB                 |              |            |                     | 1                                                |     | 1   |     |                               |

| TST    |                     |              |            |                     |                                                  |     |     | ŀ   |                               |

| STA    |                     |              | 1          | Op Code Address + 1 | 1                                                | 0   | 1   | 1   | Offset                        |

| •      |                     |              | -2         | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

|        |                     | 4            | 3          | IX + Offset         | 0                                                | 1   | 0   | 1   | Accumulator Data              |

|        |                     |              | 4          | Op Code Address + 2 | 1                                                | 0   | 1   | 0   | Next Op Code                  |

| ADDD   |                     | +            | 1          | Op Code Address + 1 | 1                                                | 0   | 1   | 1   | Offset                        |

| CPX    | LDD                 |              | 2          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

| LDS    | LDX                 | 5            | 3          | IX + Offset         | 1                                                | 0   | 1   | 1   | Operand Data (MSB)            |

| SUBD   | /-                  | -            | 4          | IX + Offset + 1     | 1                                                | 0   | 1   | 1   | Operand Data (LSB)            |

| 0000   |                     |              | 5          | Op Code Address+2   | 1                                                | 0   | 1   | 0   | Next Op Code                  |

| STD    | STS                 | +            | 1          | Op Code Address + 1 | 1                                                | 0   | 1   | 1   | Offset                        |

| STX    | 0.0                 | i            | 2          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

| 017    |                     | 5            | 3          | IX+Offset           | 0                                                | 1   | 0   | 1   | Register Data (MSB)           |

|        |                     |              | 4          | IX+Offset+1         | lo                                               | 1   | 0   | 1   | Register Data (LSB)           |

|        |                     |              | 5          | Op Code Address+2   | 1                                                | 0   | 1   | 0   | Next Op Code                  |

| JSR    |                     | +            | + -        | Op Code Address + 1 | <del>                                     </del> | 0   | 1   | 1   | Offset                        |

| 33/1   |                     | 1            | 2          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

|        |                     | 5            | 3          | Stack Pointer       | 0                                                | 1   | 0   |     | Return Address (LSB)          |

|        |                     | "            | 4          | Stack Pointer - 1   | ا                                                | 1   | o   | 1   | Return Address (MSB)          |

|        |                     |              | 5          | IX+Offset           | 1                                                | 0   | 1   | 0   | First Subroutine Op Code      |

| ASL    | ASR                 | +            | + -        | Op Code Address + 1 | <del></del>                                      | ō   | 1   | 1   | Offset                        |

| COM    | DEC                 | l            | 2          | FFFF                | 1                                                | 1 1 | 1   | 1   | Restart Address (LSB)         |

| INC    | LSR                 | 1            | 3          | IX + Offset         | 1                                                | 0   | 1   | 1   | Operand Data                  |

| NEG    | ROL                 | 6            | 4          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

| ROR    |                     |              | 5          | IX+Offset           | 0                                                | 1   | 0   | 1   | New Operand Data              |

|        |                     |              | 6          | Op Code Address + 2 | 1                                                | 0   | 1   | 0   | Next Op Code                  |

| TIM    |                     |              | 1 1        | Op Code Address + 1 | 1                                                | 0   | 1   | 1   | Immediate Data                |

|        |                     |              | 2          | Op Code Address + 2 | 1 1                                              | 0   | 1   | 1   | Offset                        |

|        |                     | 5            | 3          | FFFF                | 1 ,                                              | 1   | 1   | 1   | Restart Address (LSB)         |

|        |                     | "            | 4          | IX+Offset •         | 1 1                                              | 0   | 1   | 1   | Operand Data                  |

|        |                     |              | 5          | Op Code Address + 3 | 1                                                | 0   | 1   | 0   | Next Op Code                  |

| CLR    |                     |              | + ;        | Op Code Address + 1 | + +                                              | 0   | 1 1 | 1   | Offset                        |

| 02     |                     |              | 2          | FFFF                | 1                                                | 1   | 1   | 1   | Restart Address (LSB)         |

|        |                     | 5            | 3          | IX + Offset         | 1                                                | 0   | 1   | 1   | Operand Data                  |

|        |                     |              | 4          | IX + Offset         | 0                                                | 1   | 1 0 | 1   | 00                            |